## U508: Digital filter (SM5814AS)

#### Introduction:

The SM5814AS is a digital filter LSI for digital audios, developed uniquely by NPC making use of molybdenum-gate CMOS technology. This LSI, a single-chip device, provides quadruple-oversampling output for both channels and is capable of digital attenuation on 6-bit data.

This LSI is a smaller-sized 24-pin SOP realized through employment of serial I/O format.

#### Features:

#### Structure

Molybdenum-gate CMOS

#### **Functions**

- Quadruple oversampling for both right and left channels (Input rate fs—output rate 4fs)

- Digital attenuation

- Built-in overflow limiter

- 16-bit 2-DACs/16-bit 1-DAC/I2S/18-bit output mode selection

- 16-bit serial data input/output (2's complement, MSB first)

- · Built-in crystal oscillation circuit

- Clock output (2-divided XTI and undivided output selectable)

- Compatible with any of system clocks 384fs, 392fs, 192fs and 256fs

(However, in the I2S output mode, 392fs is unusable.)

#### Configuration

- Linear-phase FIR filter n 2 stages (105-order + 21-order)

- Reduced rounding error through employment of 18-bit filter coefficient

- Highly accurate operation by 16 x 18-bit multiplier and 25bit accumulator

- 64-step digital attenuation

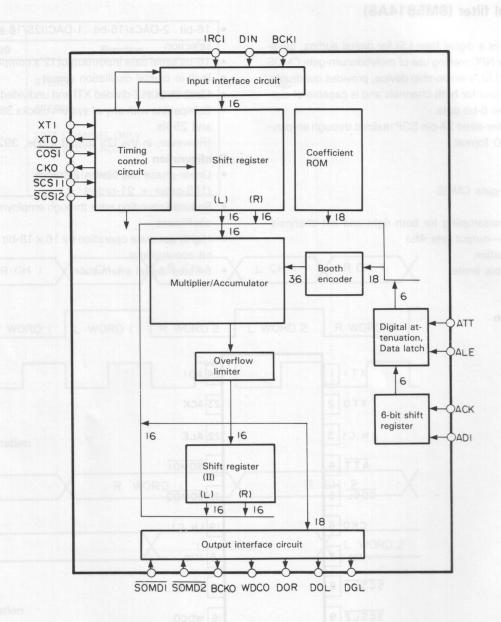

## Block diagram

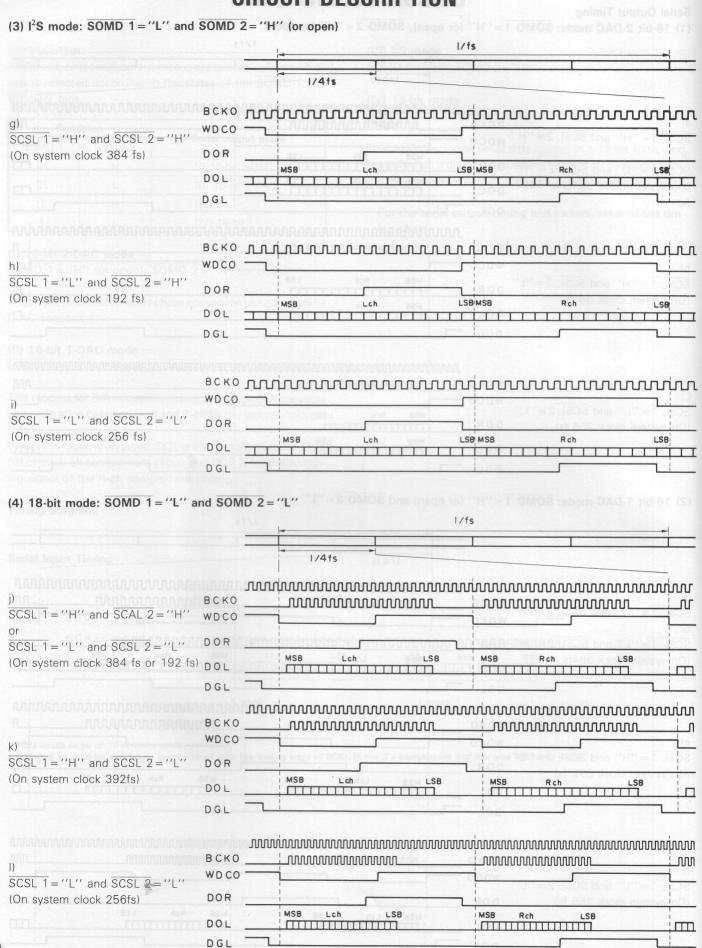

Pin Functions: Note: I: Input pin (Ip: input pin with pull-up resistor), O: Output pin

| Pin No. | Pin Name | I/O | Function                                                                                                           |  |

|---------|----------|-----|--------------------------------------------------------------------------------------------------------------------|--|

| 101     | XTI      |     | Crystal oscillation input pin (Clock input pin)                                                                    |  |

| 2       | XTO      | 0   | Crystal oscillation output pin                                                                                     |  |

| 3       |          | 1   | (N·C)                                                                                                              |  |

| 4       | ATT      | lp  | Digital attenuation O/OFF selection pin  ATT = ''H'': Digital attenuation OFF  ATT = ''L'': Digital attenuation ON |  |

| 5       | COSL     | lp  | CKO output selection pin                                                                                           |  |

| 6       | ско      | 0   | Clock output pin  COSL = "H": XTI input clock 2-divided output  COSL = "L": XTI input clock undivided output       |  |

| 7       | Vss      | 1   | GND pin                                                                                                            |  |

| Pin No.   | Pin Name                 | 1/0   | Function HOUGHS HOUGH                                                           |                          |                   |                                  |  |

|-----------|--------------------------|-------|---------------------------------------------------------------------------------|--------------------------|-------------------|----------------------------------|--|

| 8         |                          |       | This I SI realizes the quan                                                     | SOSL 1                   | SOSL 2            | XTI clock                        |  |

| 0         | SCSL 1                   | lp    | connection of itear-one                                                         | Н                        | Н                 | 384 fs                           |  |

| itwise ir | senson of                |       | Input clock selection pin                                                       | H                        | Assess Loss       | 392 fs                           |  |

| 9         | SCSL 2                   | Ip    | SCSL.                                                                           | Tung SGSLL2 pins.        | Н                 | 192 fs                           |  |

|           |                          |       |                                                                                 | L                        | L                 | 256 fs                           |  |

| 10        | LRCI                     | lp    | Basic sampling rate (fs) sync clock input L-ch/R-ch→LRCI="'H"'/"L"              | pin                      | Clock inp         | ut to XTI pin                    |  |

| 11        | DIN                      | lp    | 16-bit serial data input pin (2's complem                                       | ent, MSB first)          | 1, 1, 1, 3        | 84 ts                            |  |

| 12        | BCKI                     | lp    | Input data bit clock input pin                                                  |                          | 6 1 2             | 93 Word                          |  |

| 13        | DGL                      | 0     | L-ch output data deglitch signal output p                                       | in                       |                   | 92 fs 1911                       |  |

| 14        | DOL                      | 0     | SOMD 1 = "H", SOMD 2 = "H": L-ch da<br>Others: L-ch/R-ch data reciprocal output | ata output               | 2                 | 56 fs                            |  |

| 15        | DOR                      | 0     | SOMD 1 = "H", SOMD 2 = "H": Rc-h da<br>Others: R-ch output data deglitch signal | eta output<br>output     | a TYA's is unusab | in as the system blo             |  |

| 16        | WDCO                     | 0     | Output data word clock output pin                                               | ick purcuit antection    |                   |                                  |  |

| 17        | BCKO                     | 0     | Output data bit clock output pin                                                | LSI, from the its CK     | pin, a clock to   | ottennett A latig                |  |

| 18        | VDD                      | 1     | Supply voltage pin (4.5~5.5 V)                                                  | टी प्रधानिक एउट मेरि काल | A STANBALLETT SE  | तिक एक एक प्रमान <del>(अव)</del> |  |

| 19        | Totalba prilling adderes | w hou | (N·C)                                                                           | o ayatese fun evincing   | ne wrystal escure | MULES USAIT 45 F                 |  |

| 20        | SOMD 2                   | lр    | -6.021 d8 Which o                                                               | SOMD 1                   | SOMD 2            | Output mode                      |  |

| 20        |                          |       | -6.296 dB mined                                                                 |                          | state of Hay co   | 16-bit 2 DACs                    |  |

|           |                          |       | Serial output mode selection pin                                                | Н                        | L                 | 16-bit 1 DAC                     |  |

| 21        | SOMD 1                   | lр    | III COSE                                                                        | FilonoLinkeza            | Issided Hilliam   | l <sup>2</sup> S                 |  |

|           |                          | 8.8   | Lan top HB                                                                      | Link                     | L                 | 18-bit                           |  |

| 22        | ALE                      | lp    | Attenuation data latch clock input pin                                          | Lenli                    |                   | 1 70 70 10                       |  |

| 23        | ACK                      | lp    | Attenuation data bit clock input pin                                            | I CI DANS TO BE SOME     | Latera in tal     | W A                              |  |

| 24        | ADI                      | lp    | Attenuation data input pin (6-bit serial, M                                     | SB first)                | LI DOWN LINCON    | initi a then 80                  |  |

## **Function Description**

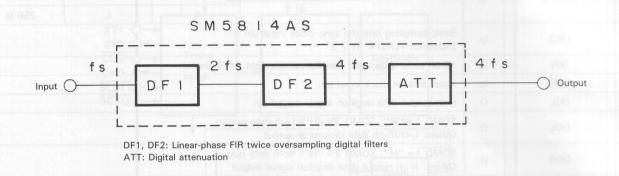

### Quadruple Oversampling:

In this LSI, the L-ch/R-ch data entered at sampling rate fs is output at sampling rate 4fs through the quadruple oversampling by digital filtering.

This LSI realizes the quadruple oversampling by the cascade connection of linear-phase FIR filters in two stages.

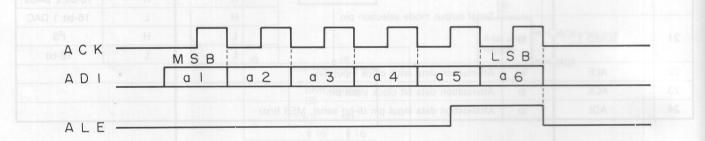

### **Digital Attenuation:**

In this LSI, the digital attenuation turns ON by making the  $\overline{\text{ATT}}$  pin ''L''.

The attenuation level is set by the 6-bit data (attenuation data) input to the ADI, ACK and ALE pins.

It is necessary that the data input to the ADI pin be represented as no-code absolute values of MSB first 6-bit serial data and be varying in synchronization with the trailing edge of the ACK.

The setting of the attenuation data on the above timing can be performed asynchronously with the digital filtering. In addition, when the  $\overline{\rm ATT}$  pin is made ''H'' (or open), the attenuation data is reset and the digital attenuation goes OFF.

The digital attenuation operation is performed by multiplying the digital-filtered data by the coefficient based upon the attenuation data.

This coefficient is generated as follows:

## Digital Attenuation Coefficient (18-bit)

a) Code bit

b) Bitwise inversion of attenuation data

c) Low-order 11 bits are all "1".

The relationship between the attenuation data and the attenuation level in this digital attenuation operation is as follows:

|    | Att | enua | tion ( | data |    | яско плипи                              |

|----|-----|------|--------|------|----|-----------------------------------------|

| a1 | a2  | аЗ   | a4     | a5   | a6 | Attenuation level                       |

| 0  | 0   | 0    | 0      | 0    | 0  | O dB                                    |

| 0  | 0   | 0    | 0      | 0    | 1  | -0.137 dB                               |

| 0  | 0   | 0    | 0      | 1    | 1  | -0.276 dB                               |

|    |     |      |        |      |    | 200000000000000000000000000000000000000 |

| 0  | 1   | 1    | 1      | 1    | 1  | -5.735 dB                               |

| 1  | 0   | 0    | 0      | 0    | 0  | -6.021 dB                               |

| 1  | 0   | 0    | 0      | 0    | 1  | -6.296 dB                               |

|    |     |      |        |      |    | DOI MSG Lo                              |

|    |     |      |        |      |    |                                         |

| 1  | 1   | 1    | 1      | 1    | 0  | -30.103 dB                              |

| 1  | 1   | 1    | 1      | 1    | 1  | -36.124 dB                              |

Level [dB] =  $20 \times \log (64-DATA)/64$ )

Level: Attenuation level Data: Attenuation data

## Serial Input:

## (1) Correspondence between LRCI polarity and data

In this LSI, the discrimination between L-ch and R-ch is made by the LRCI polarity to take data in. The correspondence between the LRCI polarity and the data is as follows:

L-ch/R-ch → LRCI "H"/"L"

#### Clock:

## (1) Clock input selection

The system clock of this LSI is a crystal oscillator or an external clock input to the XTI pin. Which clock frequency is input to the XTI pin is determined depending upon the states of the  $\overline{\text{SCSL}\ 1}$  and  $\overline{\text{SCSL}\ 2}$  pins.

| Cond   | dition   |                        |  |  |

|--------|----------|------------------------|--|--|

| SCSL 1 | SCSL 2   | Clock input to XTI pin |  |  |

| Н      | Н        | 384 fs                 |  |  |

| Н      | na L (Vn | 392 fs                 |  |  |

| L      | Н        | 192 fs                 |  |  |

| L      | L        | 256 fs                 |  |  |

fs: Input sampling rate

Note: When the I<sup>2</sup>S mode is engaged, 392fs is unusable as the system clock.

#### (2) Clock output selection

In this LSI, from the its CKO pin, a clock is output for the signal processing LSI, etc. Using this clock output, it is easier to realize a system for which one crystal oscillation is used as the master clock.

Which clock frequency is output from the  $\overline{\text{CKO}}$  pin is determined depending upon the state of the COSL pin as follows:

$\overline{\text{COSL}} = \text{''H''}$  (or open): 2-divided output of XTI input clock  $\overline{\text{COSL}} = \text{''L''}$  : Undivided output of XTI input clock

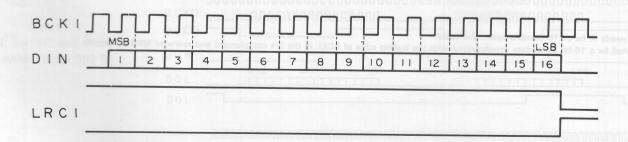

## (2) Serial data input

In this LSI, the 16-bit serial data is taken into a 16-bit shift register at the leading edge of BCKI, in the 2's complement and MSB first mode. Then, the data is latched into the data latch by the level change of LRCI at 16 bits/word separately for L-ch and R-ch. At this time, the discrimination between L-ch and R-ch is performed by the level of LRCI.

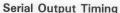

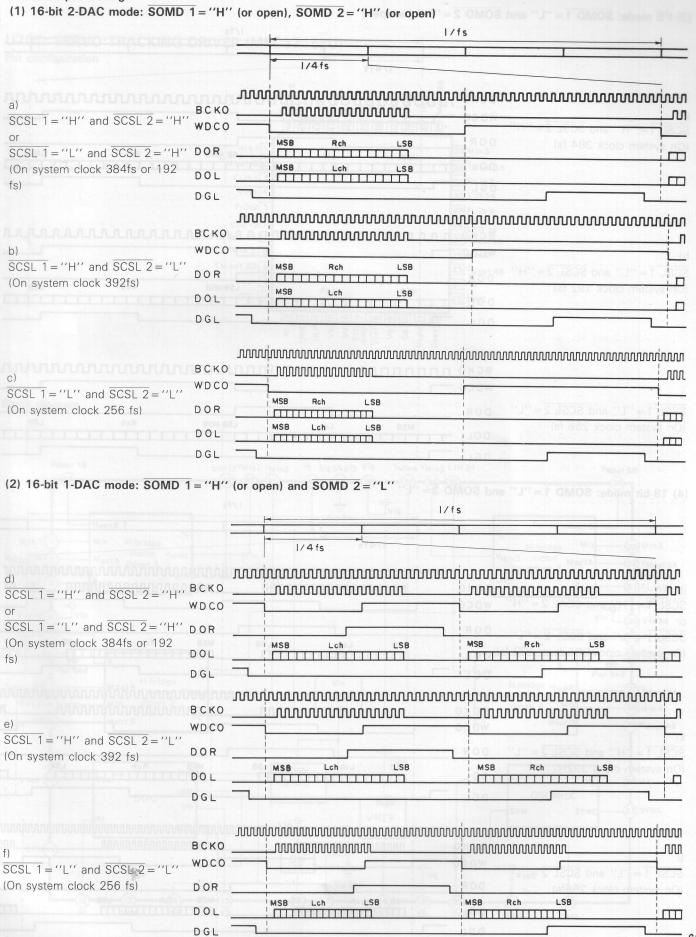

## **Serial Output:**

In this LSI, four serial output modes are available, from which one is selected according to the states of the  $\overline{\text{SOMD 1}}$  and  $\overline{\text{SOMD 2}}$  pins.

| Cond                            | dition          | 200 \$ 1202 606        |  |  |

|---------------------------------|-----------------|------------------------|--|--|

| SOMD 1                          | SOMD 2          | Serial output mode     |  |  |

| H <sub>alm</sub> <sub>173</sub> | of full-History | (I) 16-bit 2-DAC       |  |  |

| Н                               | L               | (II) 16-bit 1-DAC      |  |  |

| L                               | et Per Has      | (III)   <sup>2</sup> S |  |  |

| L los                           | L               | (IV) 18-bit            |  |  |

#### (I) 16-bit 2-DAC mode

$\overline{\text{SOMD 1}} = \text{"H" (or open)}, \overline{\text{SOMD 2}} = \text{"H" (or open)}$

This mode is for L-ch/R-ch in-phase conversion using two 16-bit D/AC converters.

#### (II) 16-bit 1-DAC mode

$\overline{\text{SOMD 1}} = \text{"H" (or open)}, \overline{\text{SOMD 2}} = \text{"L"}$

This mode is for D/A conversion using one 16-bit D/A converter and separation between L-ch and R-ch by the sample-hold circuitry.

When this mode is engaged, DGL is used for the switching signal of the L-ch sample-hold circuit and DOR is for the switching signal of the R-ch sample-hold circuit.

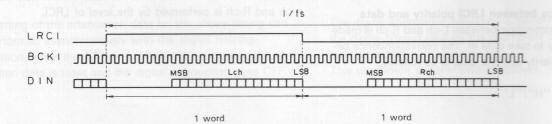

#### Timing Diagram:

## Serial Input Timing

· BCKI needs to be of 16 or more cycles per word.

• DIN shall be a 16-bit serial data synchronized with the trailing edge of BCKI, in the 2's complement and rearwise MSB first mode.

## (III) I2S mode

SOMD 1 = "L", SOMD 2 = "H" (or open)

#### (IV) 16-bit mode

SOMD 1 = "L", SOMD 2 = "L"

This mode performs serial data output in a 18-bit form, and is used when a digital attenuator is used, thereby suppressing the reduction in dynamic range due to the digital attenuation.

\* For the serial output timing and format, refer to the timing chart.