# NENTECHNICAL THEORY FOR SERVICING

# TCD-D8 CIRCUIT OPERATION (BASIC OPERATION, CIRCUIT OPERATION)

DIGITAL AUDIO TAPE RECORDER

SONY®

# **TABLE OF CONTENTS**

#### **BASIC OPERRATION**

| Sec        | tion                     | <u>Title</u> <u>Page</u>                                                 | ! |

|------------|--------------------------|--------------------------------------------------------------------------|---|

| CH/        | APTEF<br>What            | R 1. DIGITAL AUDIO TAPE RECORDER SYSTEM is DAT5                          |   |

| 1.2        | Analo<br>1.2.1           | g Recording and Digital Recording6 Analog Recording6                     |   |

| 1.3        | 1.2.2<br>Digita          | Digital Recording7<br>lization Procedure8                                |   |

|            | 1.3.1<br>1.3.2           | Digitalization of Waveform8 Sampling8                                    |   |

|            | 1.3.3                    |                                                                          |   |

| CHA<br>2.1 | APTE                     | R 2. DAT (R-DAT) SYSTEM STANDARDS Standards of DAT11                     |   |

|            | 2.1.1<br>2.1.2           | DAT Mode                                                                 |   |

| 2.2        | Rotary                   | / Head Method (R-DAT)14                                                  |   |

|            | 2.2.1<br>2.2.2           | Helical Scan Method                                                      |   |

|            | 2.2.3<br>2.2.4           | Drum Diameter                                                            |   |

| 2.3        | DAT 1                    | ape Format                                                               |   |

|            |                          | R 3. DAT ERROR CORRECTION                                                |   |

| 3.1        | ERRO                     | PR CORRECTION METHOD AND INTERLEAVE 22 Why Error Correction is Important |   |

|            | 3.1.2                    | Characteristic of Error Correction Code22                                |   |

| 3.2        | 3.1.3<br>Duple           | Interleave         23           x Reed Solomon Code         24           |   |

| 4.1        | NPTER<br>8-10 N<br>4.1.1 | 4. DAT MODULATION METHOD AND TRACKING Modulation Method and Overwriting  |   |

|            | 4.1.2                    | Required of Modulation method                                            |   |

|            |                          | Method         27           Outline         27                           |   |

|            | 4.2.2<br>4.2.3           | Detection of Tracking Error29                                            |   |

| CHA        | DTE                      | R 5. SUB CODES                                                           |   |

| 5.1        | Sub C                    | ode Format32                                                             |   |

| 5.3        | Sub C                    | odes of Main Data Area35 odes of Sub Data Area37                         |   |

|            |                          | odes of Sub Data Section39                                               |   |

|            |                          | R 6. DAT CASSETTE AND TAPE res of DAT Cassette40                         |   |

| 6.2        | Struct                   | ure of DAT Cassette40                                                    |   |

|            |                          | R 7. DIGITAL AUDIO INTERFACE                                             |   |

| 7.2        | Forma<br>7.2.1           | ıt44                                                                     |   |

|            | 7.2.2                    |                                                                          |   |

|            |                          | •                                                                        |   |

| 8.1        | SCMS                     | R 8. OUTLINE OF SCMS  Method in Different Uses46                         |   |

|            |                          | ssing Routine of SCMS Method48 Council Complying Products and SCMS       |   |

|            |                          | lying Products49                                                         |   |

# **CIRCUIT OPERATION**

| 20                   | 11110                                                                                                                                                              | Page   |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1.                   | DIAGRAMS                                                                                                                                                           |        |

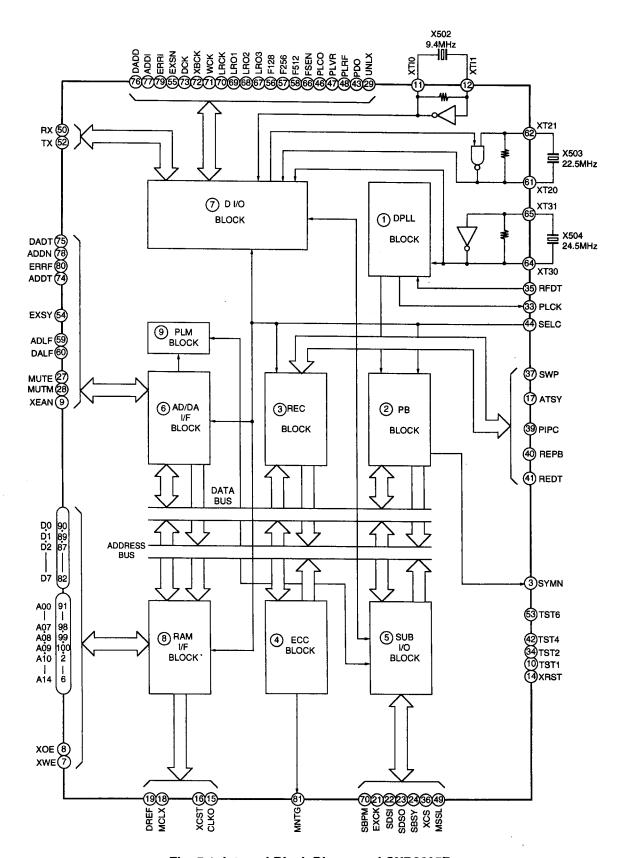

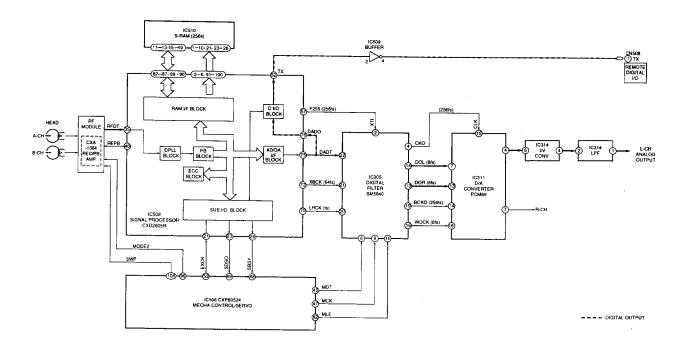

| 1-1                  | I. Block Diagrams                                                                                                                                                  | 50     |

| 2.                   | FUNCTIONS AND FEATURES                                                                                                                                             | 6·     |

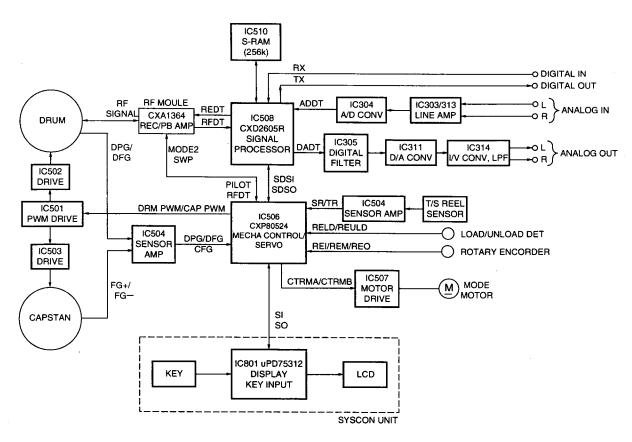

| 3.                   | SYSTEM STRUCTURE                                                                                                                                                   | 6      |

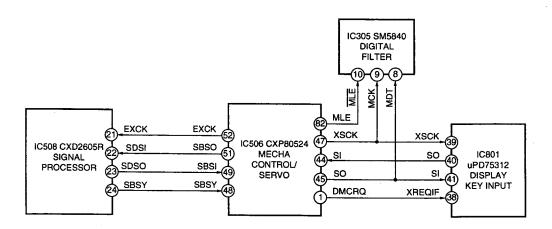

| 3-1.                 | I. Microprocessor Interface                                                                                                                                        | 64     |

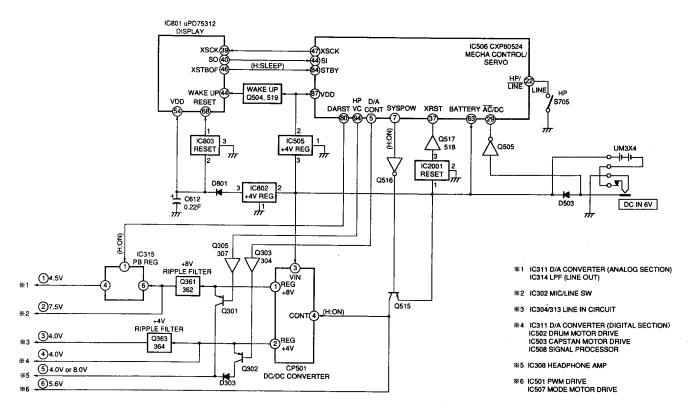

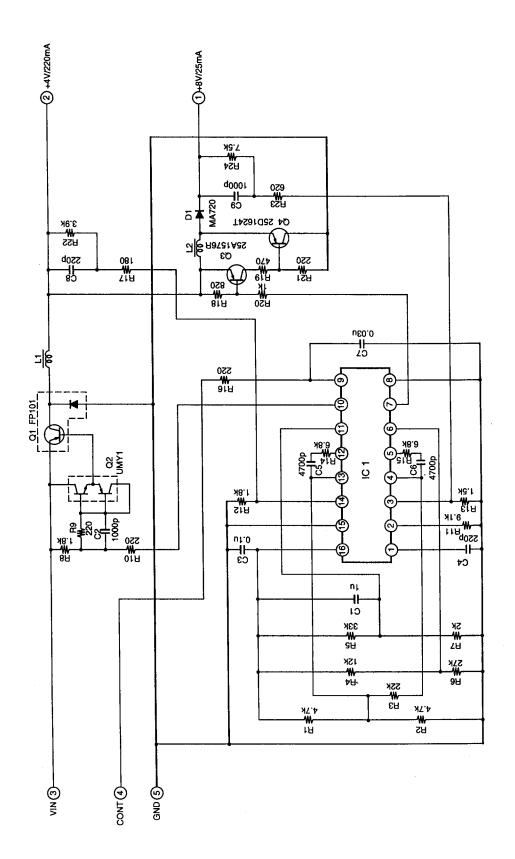

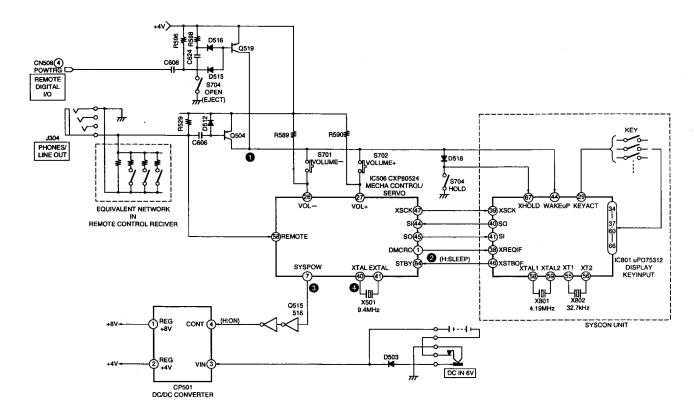

| 4.                   | POWER SUPPLY CIRCUIT                                                                                                                                               | 6      |

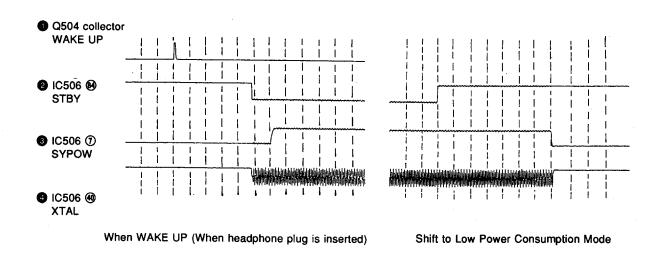

| 4-2.<br>4-3.         | Outline of Operations     Voltage Switching of Headphone Amplifier     DC/DC Converter (CP501)     Low Power Consumption Mode and WAKE U                           | 66     |

| 5.                   | SIGNAL CIRCUIT                                                                                                                                                     | 70     |

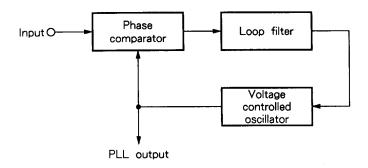

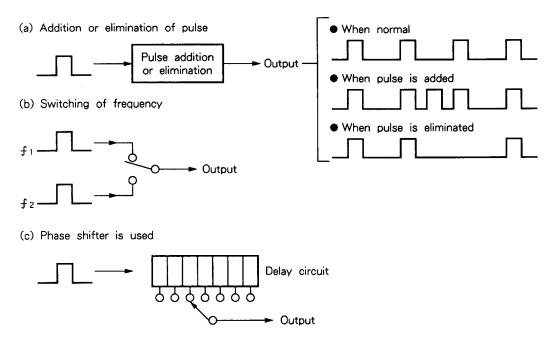

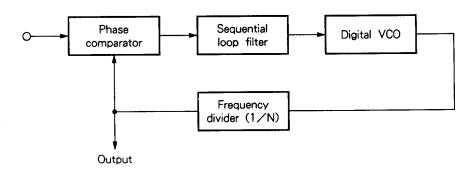

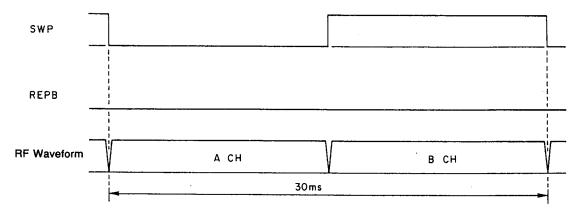

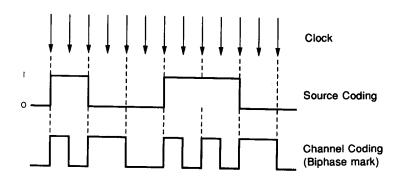

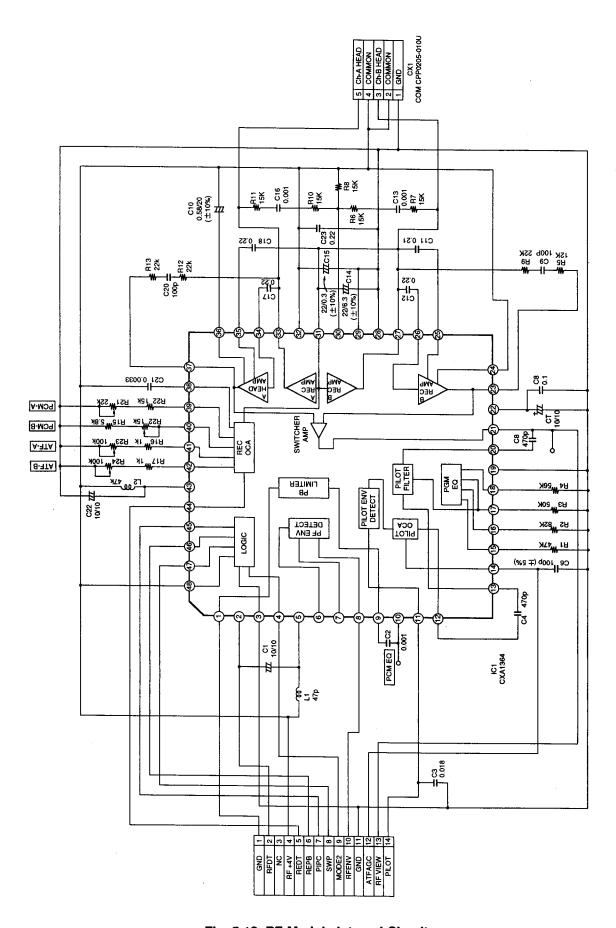

| 5-2.<br>5-3.<br>5-4. | Signal Processing LSI (CXD2605R)     Digital PLL Circuit (Reference)     Clock System     Operations During Recording     Operations during Playback     RF Module | 75<br> |

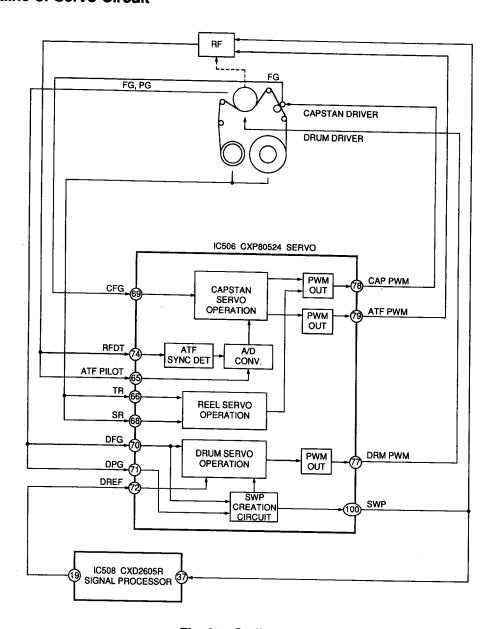

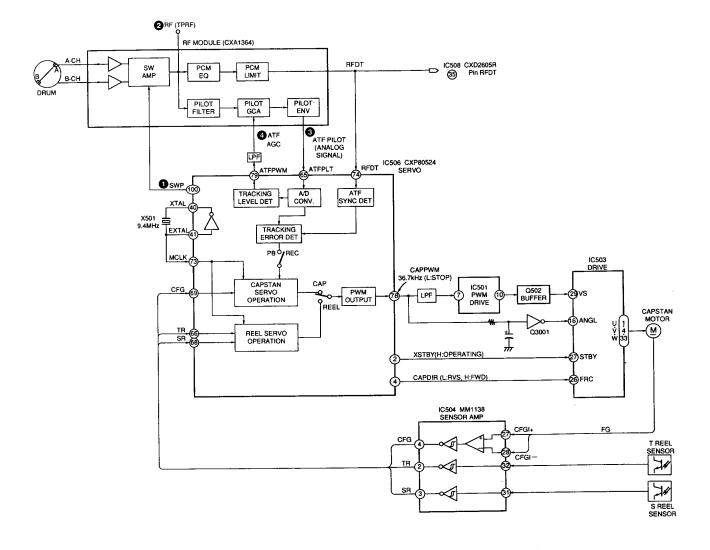

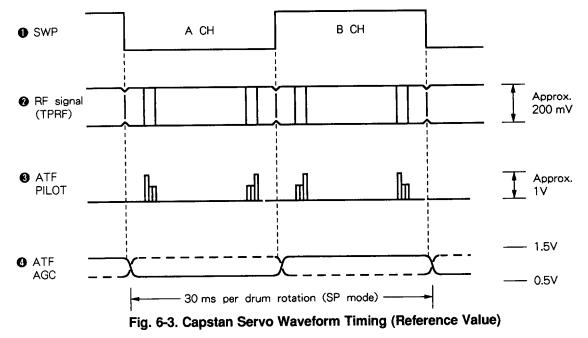

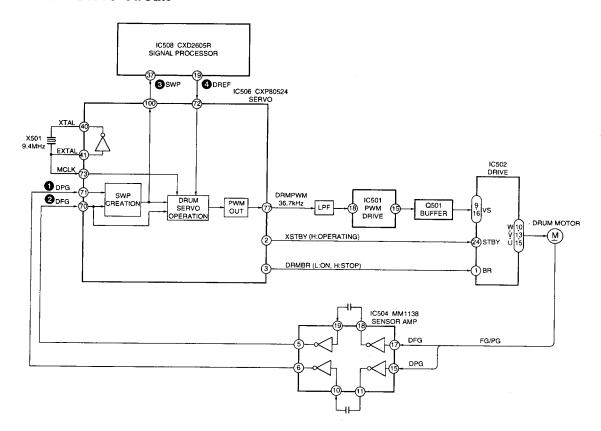

| 6.                   | SERVO CIRCUT                                                                                                                                                       | 85     |

| 6-2                  | Outline of Servo Circuit     Capstan (Reel) Servo Circuit     Drum Servo Circuit                                                                                   | 87     |

| <b>7</b> .           | MECHANICAL CONTROL CIRCUIT                                                                                                                                         | 92     |

| 7-2.                 | . Mode Motor Control                                                                                                                                               | 95     |

| 8.                   | OPERATIONS OF MECHANISM                                                                                                                                            | 98     |

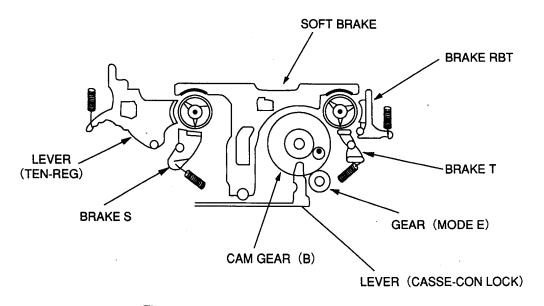

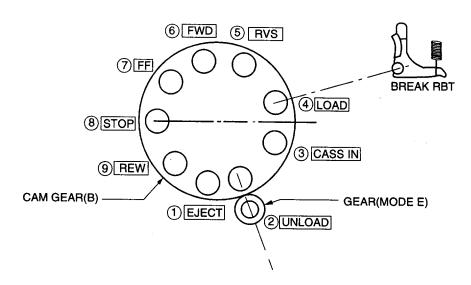

| 8-1.<br>8-2.         | . Brake and Cam Gear (B) of Mechanism<br>2. Timing of Shift to Modes                                                                                               | 98     |

|                      |                                                                                                                                                                    |        |

# **CHAPTER 1. DIGITAL AUDIO TAPE RECORDER SYSTEM**

The digital audio tape recorder system is normally called DAT system, by taking its initials. This chapter describes this DAT system, its mechanism, and merits.

#### 1.1 What is DAT

DAT is a system which recounts sound waveform using binary numbers "1" and "0" (by digitalization) to record on and play back tapes. This chapter will mainly describe the rotary head digital audio tape recorder DAT (R-DAT: Rotary Head Digital Audio Taperecorder) which was commercialized in March 1987 and is currently the most widely used DAT system. The features of this DAT system are as follows.

- (1) 16-bit multi fs

- 16-bit linear quantization → high sound quality equivalent to CDs, and applicable for non-consumer uses as well

- 48k, 44.1k, 32 kHz sampling frequencies (fs)

- → Directly digital-connectable to various types of digital equipment

- (2) High density recording

- · Helical scan method using rotary head

- → ø 30 (15) mm drum, Ach/Bch (2 heads)

- Guard bandless azimuth recording → Recording density 114 MBPI<sup>2</sup>

- 90° lap mechanism discontinuous recording by time axis compression

- (3) High reliability

- Highly efficient error correction coding (Duplex Reed-Solomon code)

- Block-complete interleave → Completed with 2 tracks, numerous functions for editing

- ATF tracking servo → Fixed head (CTL head) not required

- Overwritable → Erasure head not required

- (4) Multiple functions

- High sub-code area → Start ID, program No., etc. (200 Kbits/s)

- Area-divided format → After-recordable sub-code

- High speed access by 90° lap shallow-winding mechanism (x200 faster than playback in some models)

- (5) Compact cassette

- · Use of metal tape and flangeless cassette enables continuous recording for two hours

- · Completely sealed structure incorporating hub brake system and end detection prism

- (6) Wide application

- · Applicable to Walkman, HiFi audio, Non-consumer data recorder

- Various uses with extended play, 4 channels, wide track, etc.

- → Takes into consideration diverse needs and mass production of software tapes.

# 1.2 Analog Recording and Digital Recording

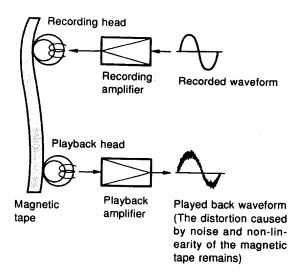

#### 1.2.1 Analog Recording

The conventional tape recorder, as shown in Fig. 1.1, converts amplitude waveform of sound signal currents directly to magnetic flux density\*1 proportionate to the amplitude of the current. The magnetic flux density of the tape is also taken as the changes in the current in playback. Consequently, when large amplitude currents are supplied, magnetic saturation\*2 prevents proportionate magnetic flux density from being obtained, causing sound distortion and small amplitudes to be hidden behind tape noises. Moreover, the driving force of the tape has slight rotation inconsistency, thus leading to irregular speed of tape running and to wow flutter\*3 in which the sound is vague or shaky.

There is, therefore, a limitation to performance with analog playback which records and plays back sound signal currents continuously and regardless of the amplitude.

Fig. 1.1 Analog Tape Recording/Playback System

- \*1...Magnetic density

- : The magnetic lines of force from the magnet are drawn from the N pole to the S pole, and are believed to flow together in a mass. This is called magnetic flux. The amount of magnetic flux per unit area (1 m<sup>2</sup>) is called magnetic flux density.

- \*2...Magnetic saturation: The magnetic flux density increases proportionately to the strength of the magnetic field until a certain level, beyond which it will not increase even if the magnetic field is made stronger. This phenomenon is called magnetic saturation.

- \*3...Wow flutter

- : Wow flutter is the changes in the speed of the tape in the tape recorder or the rotating speed of the record player in a certain period.

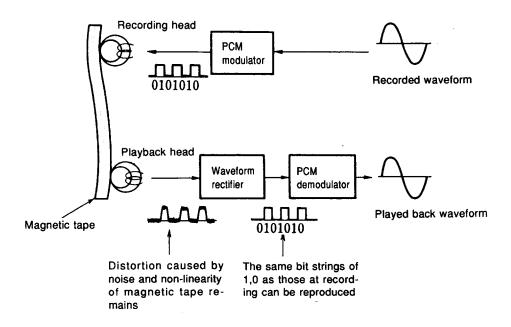

#### 1.2.2 Digital Recording

With the digital recording format, continuous sound waveform signals are divided according to as shown in the top drawing of **Fig. 1.2**, and the amplitude of the waves is remeasured by binary numbers "1" and "0", where "1" is taken as "current flows" while "0" is taken as "no current flows", and the signals are recorded on the magnetic tape as "magnetic changes" and "no magnetic changes". During playback, this presence/absence of magnetic changes on the tape corresponds to the presence/absence of current flowing to the coil, and the amplitude of the current is calculated to reproduce the original sound signal currents.

During this process, between recording performed with the recording head and playback with the playback head, only "presence/absence of current" and "presence/absence of magnetic changes" will be taken into consideration in recording and playback. Therefore even if distortion and noises mix and disturb the waveform, or the rotation becomes inconsistent and disturbs the waveform, as long as the waveform is rectified to the original waveform as shown at the bottom of Fig. 1.2, the sound signal waveform can be reproduced correctly. This is one of the greatest feature of digital recording.

Fig. 1.2 Digital System Tape Recording/Playback System

# 1.3 Digitalization Procedure

#### 1.3.1 Digitalization of Waveform

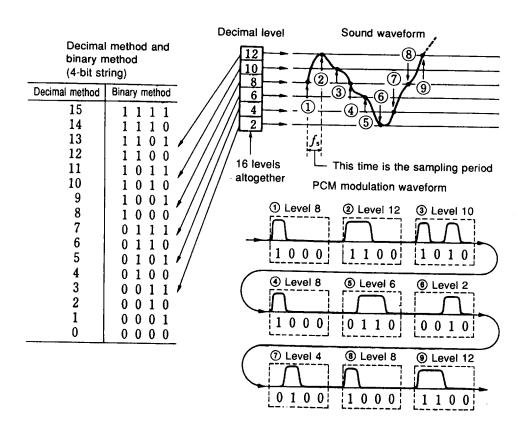

First sound signal waveform is converted to binary numerical rows. As shown in **Fig. 1.3**, how closely the original waveform can be reproduced depends on how much interval to leave between the sound signal waveform (sampling) and how accurately the waveform is read (quantization).

Fig. 1.3 Sound Signal Waveform (Analog) Digitalization Processing Procedure

#### 1.3.2 Sampling

Sampling means how minutely the horizontal time axis of the sound signal waveform is divided. The number of waveform read in one second is called the sampling frequency (fs is the symbol). To reproduce the waveform as closely as possible, it is necessary to divide and read the changes as minutely as possible so that these changes can be tracked. As a rough approximate, it has been recommended that a sampling frequency more than twice the frequency of the sound waves to be reproduced be selected, according to the sampling theorem.

For example, if the sampling frequency is set as 48 kHz (the sound waveform in one second is divided into 48000 and read), 1/2 of this (24 kHz) becomes the upper limit of the playback frequency range. Consequently, the sound signals below this frequency can be more or less reproduced closely, but not for signals above this frequency.

#### 1.3.3 Quantization

Quantization means how minutely the amplitude of vertical axis of sound waveform signals is divided in binary.

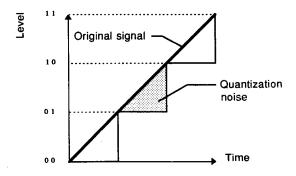

When between the maximum positive and negative values of sound waves are quantized for example, **Fig. 1.4** shows when quantization is performed with 2 bits (represented by a combination of two "0"s and "1"s), **Fig. 1.5** shows when quantization is performed with 3 bits (represented by a combination of three "0"s and "1"s.)

Original signal

Original signal

Quantization noise

Time

Fig. 1.4 2-Bit Quantization

Fig. 1.5 3-Bit Quantization

As shown in the above figure, the value after quantization is not the actual amplitude of the original signal waveform for the difference in the amplitude of the original signal. This difference is called the quantization noise (or quantization distortion). It is a type of noise peculiar to the digital system which always occurs during digitalization.

The size of this quantization noise decreases as the quantization bit is increased. The scale accuracy doubles as the bit increases by one so that the difference with the amplitude of the original signal becomes 1/2.

For example, if 16-bit linear quantization is performed, the scale becomes as detailed as  $2^{16} = 65536$ .

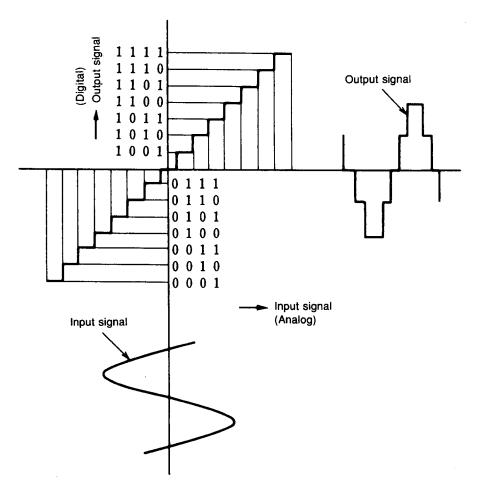

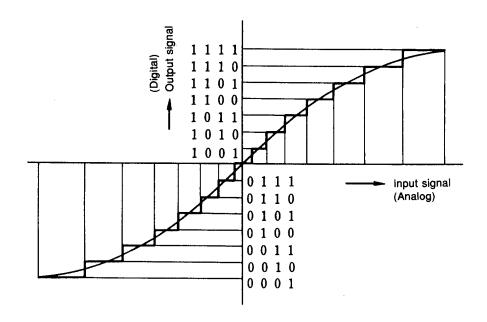

For this reason, the method of quantization which measures the amplitude of the original signal at equal intervals using a binary scale is called **linear quantization**. **Fig. 1.6** shows the input/output characteristics of linear quantization.

In respect to this, to divide the strength of a certain sound with a few bits (to use as little bits as possible), taking into consideration the nature of the hearing of human beings and the nature of sound signals, as shown in Fig. 1.7, the scale is made fine where the amplitude is small and rough where the amplitude is great. This is called **non-linear quantization**. With non-linear quantization, the quantization noise is small at small signal levels and great at high signal levels, and the noise level changes according to the input signal level. These methods are adopted because noises which increase to a certain level when signal levels are high cannot be heard by the hearing of human beings.

Fig. 1.6 Input/Output Characteristics of Linear Quantization

Fig. 1.7 Input/Output Characteristics of Non-Linear Quantization

# **CHAPTER 2. DAT (R-DAT) SYSTEM STANDARDS**

This chapter describes the main standards of DAT.

#### 2.1 Main Standards of DAT

#### 2.1.1 DAT Mode

The DAT system has six modes as shown in **Table 2.1**. The features of these six modes are described in the following. Take note that, unlike analog recording, no sounds will be played back in digital recording if the wrong mode is used.

- (1) 48k mode: The recording and playback standard mode and sampling frequency is 48 kHz, the quantization bit number is 16 bits, and linear quantization is used.

- The tape speed is 8.15 mm/s, enabling two hours of continuous recording. Most of the DAT systems are equipped with not only analog input/output but digital input/output as well, enabling mutual digital dubbing.

- © Best suited for satellite broadcast B mode recording and playback.

- (2) 44k mode:Recording and playback enable. The sampling frequency and quantization bit are the same as CDs. The tape speed and recording time are the same as the 48k mode.

- ® Best suited for recording and playback of CD and MD software discs and DAT software tapes.

- (3) 44k-WT mode: **Playback only mode**. WT stands for Wide Track Pitch. In this mode, the tape speed is 1.5 times the standard speed which is 12.225 mm/s. The track width is also expanded by 1.5 times. This mode is provided especially for contact printing, which can be applied for the mass production of software tapes. The insufficient output of the contact-printed tapes is supplemented by widening the track width. The playback time is 80 minutes.

- (4) 32k mode:Optional mode. The sampling frequency is 32 kHz and the quantization bit number is 16 bits. Linear quantization is used. It enables recording to be performed

without degrading the quality of the PCM broadcast in any way.

As the tape speed is 8.15 mm/s, recording and playback of two hours can be performed.

Suitable for recording signals input from digital inputs directly.

© Best suited for the recording and playback of the satellite broadcast A mode.

- (5) 32k-LP mode: Optional mode. LP stands for Long Play.

- The sampling frequency is 32 kHz and the quantization bit number is 12 bits. Non-linear quantization is used.

By compressing the quantization bit number to 12 bits, the recordable time is doubled to four hours.

Compared to the standard 48 kHz and 16 bits, the 32 kHz and 12 bits information volume per channel is exactly half from the following, thus enabling extended recording of two times.

$48 \text{ kHz} \times 16 \text{ bits} = 78 \text{ kbits/s} = 2 \times 32 \text{ kHz} \times 12 \text{ bits}$

(6) 32k-4ch mode: Optional mode. Pair mode with 32k-LP mode.

The information volume decreased by adopting 12-bit non-linear quantization is used for increasing the number of channels.

This mode has the same tape speed as the 48k mode, enabling the recording of signals of 4 channels.

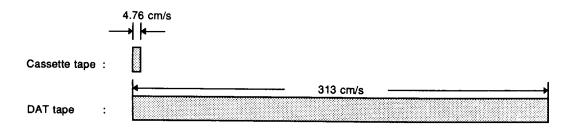

# 2.1.2 Comparison with Compact Cassette Tape

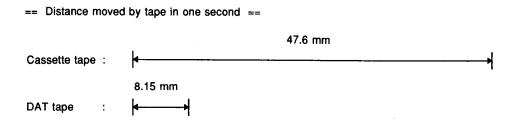

Compared to the tape speed of analog compact cassette tape speed (4.76 cm/s);

② Tape speed: About 1/6 times with 8.15 mm/s → Low tape consumption amount, high speed FF/REW (See Fig. 2.2)

Fig. 2.1 Comparison of Cassette Tape and DAT Tape Relative Speeds

Fig. 2.2 Comparison of Cassette Tape and DAT Tape Speeds

Table 2.1 Main Standards of Modes Used in DAT Systems

|                            | Mo             | ode          |                          | Recor         | ding and Playback | Mode            |               | Playback Only Mode |  |  |  |

|----------------------------|----------------|--------------|--------------------------|---------------|-------------------|-----------------|---------------|--------------------|--|--|--|

| Item                       |                |              | 48k mode                 | 32k mode      | 32k-LP mode       | 32k-4ch mode    | 44k mode      | 44k-WT mode        |  |  |  |

| Channel no. (ch)           |                |              | 2                        | 2             | 2                 | 4               | 2             | 2                  |  |  |  |

| Sampling fre               | quency (kHz    | )            | 48                       | 44            | .1                |                 |               |                    |  |  |  |

| Quantization bit no. (bit) |                |              | 16 (Linear)              | 16 (Linear)   | 12 (Non-linear)   | 12 (Non-linear) | 16 (Linear)   | 16 (Linear)        |  |  |  |

| Linear record              | ding density   | (kbpi)       | 61.0                     |               | 61.0              | -               | 61.0          | 61.1               |  |  |  |

| Plane record               | ing density (l | (bpi²)       | 114                      |               | 114               |                 | 114           | 76                 |  |  |  |

| Transmission               | n rate (Mbps)  |              | 2.46                     | 2.46          | 1.23              | 2.46            | 2.4           | 46                 |  |  |  |

| Sub-code cap               | pacity (kpbs)  |              | 273.1                    | 273.1         | 136.5             | 273.1           | 273           | 3.1                |  |  |  |

| Modulation 1               | method         |              |                          |               | 8-10 modul        | ation format    |               |                    |  |  |  |

| Correction m               | nethod         |              |                          |               | Duplex Reed-      | Solomon code    |               |                    |  |  |  |

| Tracking me                | thod           |              |                          |               | Area div          | ided ATF        |               |                    |  |  |  |

| Cassette size              | (mm)           |              |                          |               | 73x54             | 4x10.5          |               |                    |  |  |  |

| Recording ti               | me (min)       |              | 120                      | 120           | 240               | 120             | 120           | 80                 |  |  |  |

| Tape width (mm)            |                |              | 3.81                     |               |                   |                 |               |                    |  |  |  |

| Tape type                  |                |              | Metal powder Oxidation t |               |                   |                 |               |                    |  |  |  |

| Tape thickne               | ess (µm)       |              | 13±1                     |               |                   |                 |               |                    |  |  |  |

| Tape speed (               | (mm/s)         |              | 8.15                     | 8.15          | 4.075             | 8.15            | 8.15          | 12.225             |  |  |  |

| Track pitch                | (μm)           |              |                          | 20.41         |                   |                 |               |                    |  |  |  |

| Track angle                |                |              | 6° 22′ 59.5″ 6° 23′ 29.4 |               |                   |                 |               |                    |  |  |  |

| Standard dru               | ım specificati | ons          | ø 30 90° lap             |               |                   |                 |               |                    |  |  |  |

| Number of r                | otation (r.p.n | 1.)          | 20                       | 20            | 2000              |                 |               |                    |  |  |  |

| Relative spe               | ed (m/s)       |              | 3.3                      | 133           | 1.567             | 3.133           | 3.133         | 3.129              |  |  |  |

| Head azimut                | th angle       |              | ±20°                     |               |                   |                 |               |                    |  |  |  |

| Remarks                    |                |              | Standard record-         | PCM broadcast | Extended re-      | 4ch             | 44.1 standard | Music tape only    |  |  |  |

|                            |                |              | ing and playback         | recording     | cording Half-     |                 | mode          | mode, suitable     |  |  |  |

|                            |                |              | mode                     |               | speed             |                 |               | for contact print, |  |  |  |

|                            |                |              |                          |               |                   |                 |               | playback only      |  |  |  |

| Current                    | Recording      | Analog       | 0                        | ×             | 0                 | х               | X*1           | ×                  |  |  |  |

| general                    |                | Digital      | 0                        | 0             | 0                 | X               | 0             | X                  |  |  |  |

| DAT                        | Play           | back         | 0                        | 0             | 0                 | x               | 0             | 0                  |  |  |  |

| Characterist               | tics Freque    | ncy response | 22 kHz                   | 14.5 kHz      | 14.5 kHz          | 14.5 kHz        | 20 kHz        | 20 kHz             |  |  |  |

<sup>\*1:</sup> DTC-A7, DTC-A8, DTC-60ES, DTC-2000ES, and TCD-D8 can record at sampling frequencies of 44.1 kHz.

# 2.2 Rotary Head Method (R-DAT)

# 2.2.1 Azimuth Guard Bandless Recording Method

The azimuth guard bandless recording method is the best method for increasing recording density.

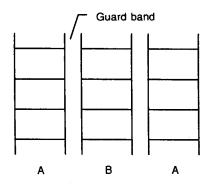

To explain the theory briefly; With the current recording method using the guard bands, as shown in Fig. 2.3, to prevent the mixing of signals by tracking deviation during playback due to the recording of heads A and B at the same angle, guard bands are used to create space.

Fig. 2.3 Recording Method Using Guard Bands

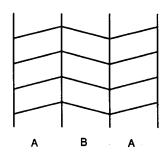

With the azimuth guard bandless recording method, by tilting heads A and B in the opposite direction to the direction in which they move as shown in **Fig. 2.4**, signals of track B will not be played back by head A and the signals of track A will not be played back by head B, thus preventing the mixing of signals. This makes the guard band between tracks A and B redundant, increases the track pitch, and consequently increases the recording density.

Fig. 2.4 Azimuth Guard Bandless Recording Method

The features of the azimuth guard bandless recording method are shown below.

- 1 Resistant to tracking error and mechanism accuracy is not critical

- ② Suited for overwriting

- 3 Suited for ATF method

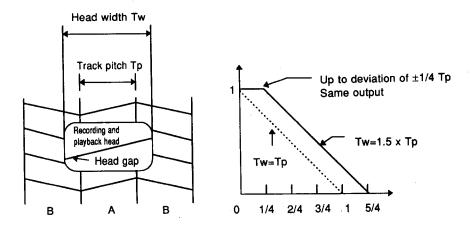

The azimuth guard bandless recording method is capable of increasing the track width for recording and playback heads above the recording track pitch as shown in the left figure of Flg. 2.5 (because of guard bandless). It is advantages in terms of compatibility because during playback, as the playback head width is wider than the track pitch, even if the tracking deviates slightly, sufficient output can be obtained. (See Fig. 2.5. Right Figure)

Fig. 2.5 Output Characteristics of Guard Bandless Recording and Wide Head

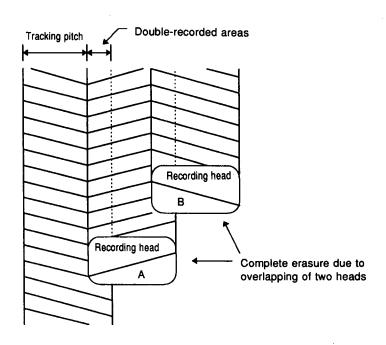

The ATF method which performs tracking by reading signals from adjoining tracks simultaneously can be performed without the need of special heads. Because the head width is wider than the recording track width, complete erasure is ensured as shown in Fig. 2.6, thus ensuring overwriting without any erasure heads.

Fig. 2.6 Recording

#### 2.2.2 Helical Scan Method

To realize further decrease in size and easy-to-use drum speed for the rotary head of the DAT system, the helical scan method (tilted scanning) which has been used most extensively in previous VTR models has been adopted.

With the helical scan method, the track is slightly tilted against the tape running direction to form a long linear track. The merits of this method are;

- (1) As the drum is slightly tilted against the tape, safe tape running and contact between tape and head can be expected.

- 2 Large diameter drums can be used with a comparatively low speed, etc.

As the track of this method is linear, systems can be designed with any drum diameter. The drum diameter is described in more detail in the following.

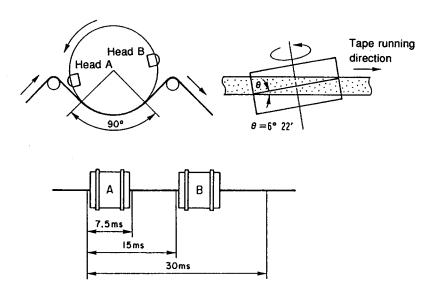

#### 2.2.3 Drum Diameter

Currently, the drum diameter of the DAT system is Ø 30 mm with a lap angle of 90° for installed units and Ø 15 mm with a lap angle of 180° for portable units. This is because the variation of the drum diameter is prescribed as follows.

øχ [mm], 2700°/χ lap angle

(Note) ø: Indicates the diameter.

Take for example the installed unit, as the diameter is 30 mm, when x is substituted with 30, the lap angle becomes  $2700/30 = 90^{\circ}$ , thus the system has a drum diameter of  $\emptyset$  30 mm with a lap angle of  $90^{\circ}$ . In this way, the system can be designed with an drum diameter as shown above.

#### 2.2.4 Definition of Track Pattern

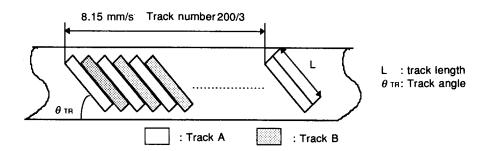

With the DAT format, the track pattern recorded on the tape is defined as shown in Fig. 2.7. As heads A and B perform recording once each with every one rotation of the drum, the track pattern is such that tracks A and tracks B are lined up orderly.

Fig. 2.7 DAT Track Pattern

With the current DAT which uses a head drum with a diameter of 30 mm, this track pattern is realized with the following specifications;

Number of head drum rotations:2000 rpm

Angle of tape winding around the head drum:90°

Angle of tilt of tape winding around the head drum in helical form (still angle  $\theta$ ): 6° 22′.

The signal waveform is an intermittent signal (discontinuous signal) which always appears at the blank portion between the signals of track A and track B (See Fig. 2.8.) because the tape winds around the head drum only for 90°.

Even if data is read from the tape discontinuously, by accumulating it in proper order on the memory and sending this data sequentially to the D/A converter, the signal can be played back as a continuous music signal. This is one feature of the DAT which records in digital.

Fig. 2.8 Drum with Diameter 30 mm

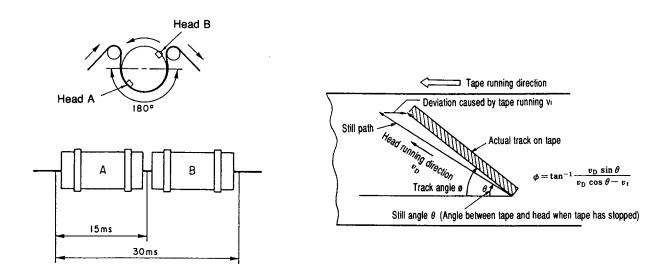

When using a head drum with a diameter of 15 mm, first to equalize the track length, since the diameter of the drum is 1/2, it is necessary to set the winding angle to  $180^{\circ}$  which is two times that of the head drum with a diameter of 30 mm. ( $\emptyset$  15 mm, lap angle of  $180^{\circ}$ ) Next, the drum is rotated at a speed of 2000 rpm, as with the drum with a diameter of 30 mm. In this case, as the relative speed is 1/2, the track angle  $\emptyset$  in **Fig. 2.10** is greater than that of the drum with a diameter of 30 mm. Therefore, the required track angle cannot be obtained with the same still angle  $\theta$  as the drum with a diameter of 30 mm.

Consequently, with the head drum with a diameter of 15 mm, the still angle  $\theta$  is made smaller than the drum with a diameter of 30 mm by about 1'.

On the other hand, the signal waveform has a shape made by expanding the waveform of the drum with a diameter of 30 mm in the time axis direction by two times as shown in **Fig. 2.9** and filling the blank portion. The basic frequency of the signal is 1/2. However, in this case, although there is a need to change the timing for reading the data from the tape, by arranging the data read on the memory, after that only the data need to be sent to the D/A converter sequentially, which makes it no different as when the drum with a diameter of 30 mm is used.

(Note) rpm: Indicates the rotation per minute.

Fig. 2.9 Drum with a Diameter of 15 mm

Fig. 2.10 Relation Between Track Angle and Still Angle

#### 2.3 DAT Tape Format

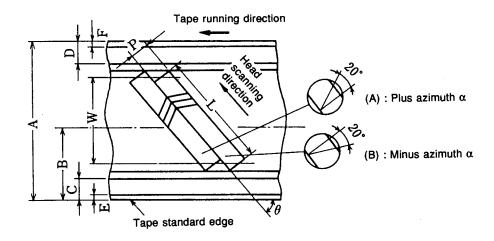

Fig. 2.11 and Table 2.2 show the DAT tape format.

First, the basic tape width (A in the figure) is  $3.81^{+0}_{-0.02}$  mm, the same tape width as the compact cassette recorder which many of us are familiar with. With the DAT system that requires precise tape running, the width tolerance standard is extremely strict, more than two times that of the compact cassette.

The effective recording width (W in the figure) is the width with which the rotary head actually records signals (approximately 2.61 mm). This means that the 0.5 mm at both edges is not used and remains as optional tracks.

With the rotary head method, the two edges of a tape is normally not used. This is because the conditions for contact between the tape and head change at the edge of the tape, resulting in difficulty in achieving safe contact between the tape and head. In addition, tape edges damage easily and data errors occur frequently.

The DAT format has high capacity by taking into consideration all of these points.

The track angle which is the most important is 6° 22′ 59.5″, and is used for all modes except the 44k-WT mode. In the 44k-WT mode, because the tape speed is 1.5 times faster, the track angle differs slightly. These measurements are all based on the lower edge of the tape. Normally, drums are equipped with a precision guide (called lead) to preserve this angle, and the tape pattern is created by having the lower edge of the tape ride onto this lead.

Fig. 2.11 DAT Tape Format

**Table 2.2 DAT Tape Format**

|   |                                 | 48k mode, 44k mode, 32k mode, 32k-LP mode, 32k-4ch mode | 44k-WT mode  |  |  |  |

|---|---------------------------------|---------------------------------------------------------|--------------|--|--|--|

| Α | Tape width (mm)                 | 3.81 (+0, -0.0                                          | 02)          |  |  |  |

| w | Effective recording length (mm) | 2.613                                                   |              |  |  |  |

| L | Track length (mm)               | 23.501                                                  | 23.471       |  |  |  |

| P | Track pitch (µm)                | 13.591                                                  | 20.41        |  |  |  |

| В | Track center (mm)               | 1.905                                                   |              |  |  |  |

| С | Optional track I (mm)           | 0.5                                                     |              |  |  |  |

| D | Optional track II (mm)          | 0.5                                                     |              |  |  |  |

| E | Edge guard I (mm)               | 0.1                                                     | ٠.           |  |  |  |

| F | Edge guard II (mm)              | 0.1                                                     | ,            |  |  |  |

| θ | Track angle (deg.)              | 6° 22′ 59.5~                                            | 6° 23′ 29.4″ |  |  |  |

| α | Head gap azimuth angle (deg.)   | ±20° (±15′)                                             |              |  |  |  |

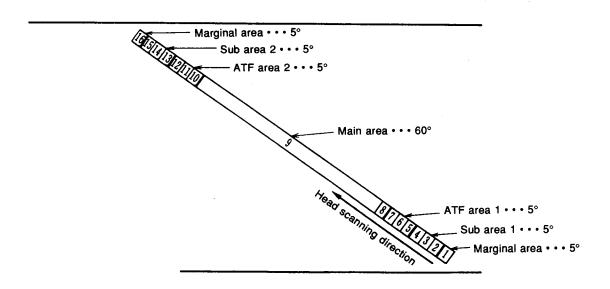

## 2.4 Arrangement of Signals on Track

With the DAT system, various signals are written on one track by dividing it into different areas. As shown in Fig. 2.12, one track is divided mainly into seven areas, and each of these areas are further divided as shown in Table 2.3. One merit of the DAT format is that editing can be performed freely by having the following independent areas.

- Main area for recording audio data

- · Sub area for recording the program-search signal

- ATF area for recording the ATF signal for tracking

Fig. 2.12 Data Arrangement on DAT track

**Table 2.3 Signal Arrangement on Track**

| Fig. No. | Area Name     | Contents        | Signal    | Angle*1 (deg.) | Block No. | Time (µS) |

|----------|---------------|-----------------|-----------|----------------|-----------|-----------|

| 1        | Marginal area | Margin 1        | 1/2 fch*3 | 5.051          | 11        | 420.9     |

| 2        |               | Preamble 1      | 1/2 fch   | 0.918          | 2         | 76.5      |

| 3        | Sub area 1    | Sub data area 1 |           | 3.673          | 8         | 306.1     |

| 4        |               | Postamble 1     | 1/2 fch   | 0.459          | 1         | 38.3      |

| 5        |               | IBG*2 1         | 1/6 fch   | 1.378          | 3         | 114.8     |

| 6        | ATF area 1    | ATF 1           |           | 2.296          | 5         | 191.3     |

| 7        |               | IBG 2           | 1/6 fch   | 1.378          | 3         | 114.8     |

| 8        | Main          | Preamble 2      | 1/2 fch   | 0.918          | 2         | 76.5      |

| 9        | Main area     | Main data area  |           | 58.776         | 128       | 4898.0    |

| 10       |               | IBG 3           | 1/6 fch   | 1.378          | 3         | 114.8     |

| 11       | ATF area 2    | ATF 2           |           | 2.296          | 5         | 191.3     |

| 12       |               | IBG 4           | 1/6 fch   | 1.378          | 3         | 114.8     |

| 13       |               | Preamble 3      | 1/2 fch   | 0.918          | 2         | 76.5      |

| 14       | Sub area 2    | Sub data area 2 |           | 3.673          | 8         | 306.1     |

| 15       |               | Postamble 2     | 1/2 fch   | 0.459          | 1         | 38.3      |

| 16       | Marginal area | Margin 2        | 1/2 fch   | 5.051          | 11        | 420.9     |

|          | Total         |                 |           | 90             | 196       | 7500      |

<sup>\*1:</sup> These figures are for the Ø 30, 90° lap drum rotated at 2000 rpm

The role of each of these areas of a track is described below.

#### (1) Marginal area

This area is located about 5° at both edges. It is a spare area provided to attain stable contact between the tape and head. No signals are recorded.

#### (2) Sub areas 1 and 2

A unique function of the DAT system, these areas are used for recording the sub-code signals (various signals such as time and address). The preamble is attached before the data signal and the postamble after the data signal. These signals are used for synchronizing with the PLL (phase locked loop) and erasing previous data in after-recording. These areas cover 5° of space in total, of which 3.7° is used for recording signals.

The sub area is divided into two areas to;

- Deal with burst error

- To make reading of data easy during high speed search

#### (3) ATF areas 1 and 2

These areas are recorded with the ATF (automatic track following) signals for tracking detection, which will be explained later.

Before and after the ATF signals, IBG (inter block gap) is provided. The IBG serves to;

- Prevent the erasure of the ATF signals even when there is signal deviation

- Cover the switching time of the recording and playback modes of the head.

#### (4) Main area

Made up of about 60°, this area is used for recording audio data converted to main digital data. It is also recorded with the parity for the audio data error correction, and the main ID (part of sub code) which records the audio data format.

<sup>\*2:</sup> IBG: Inter Block Gap. Margin space between blocks containing information recorded on the tape

<sup>\*3:</sup> Channel clock (fch=9.408 MHz) serving as standard for data recording

## CHAPTER 3. DAT ERROR CORRECTION

This chapter describes the basic concept of error correction, the most important point in handling digital data, and the error correction method used in the DAT system.

#### 3.1 ERROR CORRECTION METHOD AND INTERLEAVE

#### 3.1.1 Why Error Correction is Important

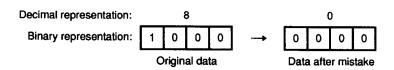

The following shows why error correction is important in the handling of digital data. As shown in **Fig. 3.1**, for "1000" which represents "8" digital data (binary data) in the decimal order, if the higher most bit "1" is mistaken as "0", the "1000" data will be mistaken as decimal "0" data in the form of "0000". In this way, as all the data will become incorrect just by mistaking one bit, error correction is has great importance.

Fig. 3.1 Example of Error

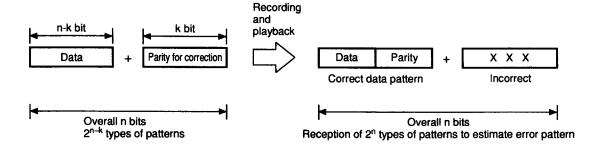

#### 3.1.2 Characteristic of Error Correction Code

The ability to completely correct data errors caused by scratched and failed tapes and discs is already familiar with CDs. In the case of DAT, the error rate per bit is 10<sup>-5</sup> to 10<sup>-6</sup> on the average. If 1.5M bits of audio data is recorded every second, it means that errors occur several times each second.

The characteristic of the error correction code is explained here briefly. As shown in **Fig. 3.2**, data for correction (k bit) is added to the data signal (n-k bit), and the correct data pattern is sent together with the n bit data containing the error pattern. But if errors occur halfway through the transmission, the data being sent will appear as various failed data, and this difference in how it appears is called distance.

Fig. 3.2 Error Correction Coding Process

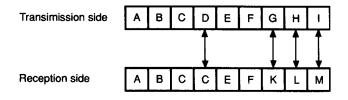

For example, if the transmission side data and reception side data differ at four locations as shown in **Fig. 3.3**, the distance will be "4". This distance is calculated at the reception side, the error position is determined, and error correction is performed.

Fig. 3.3 Distance Between Data

#### 3.1.3 Interleave

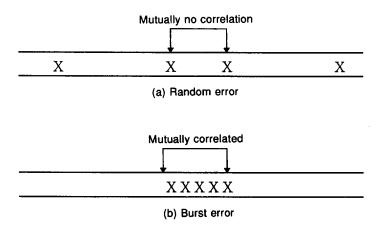

There are broadly two types of error patterns-random error and burst error. These are described briefly in the following.

- Random error ...... As shown in **Fig. 3.4** (a), these errors are generated independently, mainly due to the noise components.

- Burst error .......... As shown in Fig. 3.4 (b), these errors are generated continuously, mainly due to the failure and scratching of tapes, and deviation of synchronization.

Fig. 3.4 Random Error and Burst Error

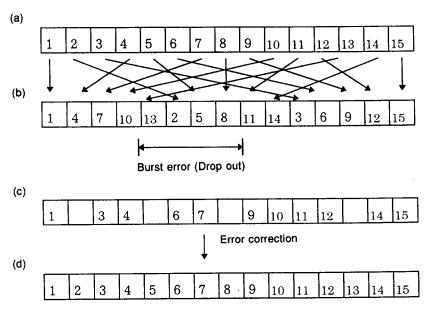

If errors occur continuously as with burst errors, a certain portion of the data will be lost to a considerable extent, consequently leading to difficulty in correction and compensation. The method thus used in such cases is interleave. The basic concept of interleave is described next.

Interleave means the work to rearrange signals according to a certain rule (method to record a group of data not together but one by one).

As shown in Fig. 3.5, as (a) and (b) are rearranged, if the burst error occurs, and it is corrected to the actual signal (deinterleave), several small random errors will be generated in scattered form as shown in (c), and thus enable the error to be estimated from the redundancy bit, and the correction shown in (d) to be performed.

If error cannot be corrected, the actual value can be estimated from the previous and following data, since the original data is an analog signal.

Fig. 3.5 Concept of Interleave

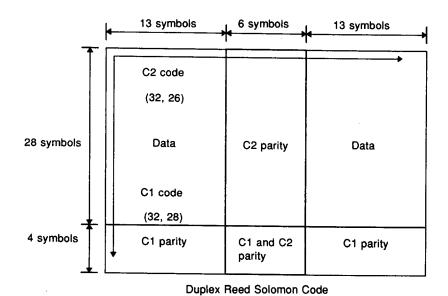

# 3.2 Duplex Reed Solomon Code

This chapter describes the duplex Reed Solomon method used by the DAT system.

As shown in Fig. 3.6, two Reed Solomon codes are combined in the vertical and horizontal directions in the DAT system. This combination is called product code.

(Note)1 symbol = 8 bits

Fig. 3.6 DAT Product Code Structure

Combining two codes in this way creates stronger resistance to random error, and enables the creation of practical codes with which errors can be corrected easily and the detection circuit can be made simple. The following shows the merits of duplex coding.

- 1 The minimum distance of codes is the product of two codes correction efficiency is extremely high

- ② As the two codes function as pointers to indicate the error positions, it enables correction of lost data and is effective for correcting burst error.

- 3 By improving the interleaving of the two codes, the codes can be used as follows, leading to higher effectiveness on the whole.

- (1) The codes in the first stage are used for correction of random error and detection of burst error.

- (2) The codes in the second stage are used for correction and interpolation of burst errors.

In addition, the duplex Reed Solomon codes need only be used in two tracks (tracks A and B).

#### CHAPTER 4. DAT MODULATION METHOD AND TRACKING

#### 4.1. 8-10 Modulation Method and Overwriting

#### 4.1.1 Necessity of Overwriting and Characteristic Required of Modulation method

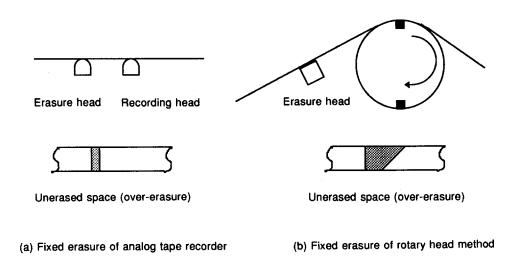

With current analog recorders, the erasure head is located at the previous position of the recording head as shown in **Fig. 4.1** (a) to erase signals previously recorded prior to recording. This is because, with analog recording, erasure by overwriting proved insufficient.

With the DAT system, as the rotary head method is adopted, the recording track is tilted. With the current fixed erasure head method, the triangular unerased space as shown in Fig. 4.1 (b) remains. With the DAT system, as the recording density is high and the tape speed is slow, this unerased space which could be ignored with the fixed erasure head method cannot be ignored because it lasts for more than 3 seconds. Thus digital recording is applied and the overwrite method is adopted.

Fig. 4.1 Unerased Space by Fixed Erasure Head

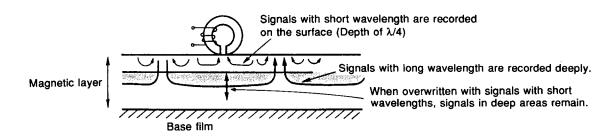

With the overwrite method, an erasure head is not provided and therefore the previously written signals are erased by the signals written next. Generally, in magnetic recording in the longitudinal direction, signals with short wavelengths are recorded on the surface of the magnetic substance while signals with long wavelengths are recorded deeply as shown in **Fig.** 4.2, which makes it therefore difficult to erase signals written with long wavelengths with signals written with short wavelengths. Consequently, the modulation method suited for overwriting must have as little long waveform components as possible.

Fig. 4.2 Overwriting

#### 4.1.2 8-10 Modulation Method

The characteristics required of the modulation method for DAT are as follows.

- 1 No direct current components for the use of rotary transformer

- 2 The spectrum is made up mainly of short wavelengths to enable overwriting

- 3 Resistant to S/N deterioration such as crosstalk and unerased areas

- Matches well with error correction method (8-bit unit processing).

The 8-10 modulation method was adopted because it satisfied these conditions.

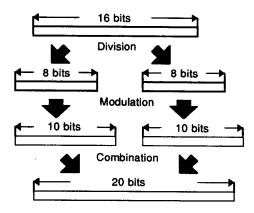

As its name implies, this method converts 8-bit data to 10-bit data to recording. As shown in Fig. 4.3, 16-bit data is divided into the **upper 8 bits** and **lower 8 bits**, and the 8-bit data is each converted to data with a few direct current components selected from the respective 10 bits. This explains why tapes are recorded with 16-bit data increased to 20-bit data.

Fig. 4.3 8-10 Modulation Method

The following describes the mechanism of the 8-10 modulation method.

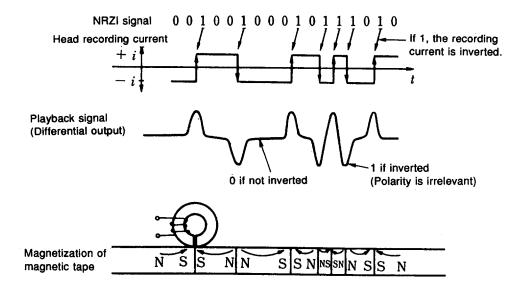

In the 8-10 modulation method, conversion is performed according to the NRZI (Non Return Zero Inverse) rule. NRZI, as shown in **Fig. 4.4**, inverts the current when "1" and outputs the recording current at it is when "0". As the direction inverted in is irrelevant, the magnetization pattern polarity can be from N pole to S pole or vice versa.

Fig. 4.4 NRZI Modulation

#### 4.2 ATF Method

#### 4.2.1 Outline

The ATF (Automatic Track Following) method is a technology which automatically imposes servo using the rotary head and traces the target track.

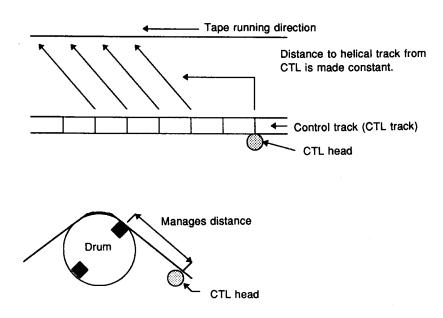

Until now, the control track method (CTL method in short) was used for the rotary head method. As shown in Fig. 4.5, with the CTL method, a CTL track is provided at the edges of the tape independently from the rotary head, and CTL signals are recorded with a fixed head separately from the rotary head. During playback, the signals of the CTL track are read to control the tape feed phase so that the rotary head traces the recorded track in the same way during recording. However, because it is an indirect method using the fixed head, the tracking position shifts due to the position of the fixed head and the extension and contraction of the tape, the method is not suitable for high density recording.

Fig. 4.5 Control Track Method

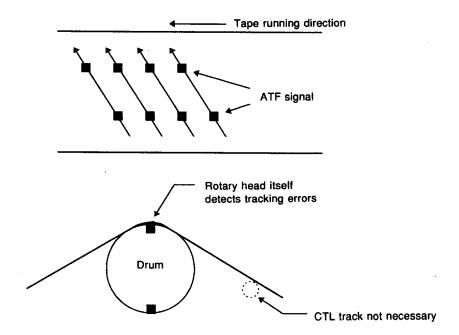

With the ATF method, signals recorded by the rotary head are recorded together with tracking signals as shown in Fig. 4.6, and during playback, the rotary head itself detects the tracking signal to calculate its own head position and sends the error signal to the capstan motor.

The following are the merits of the ATF method.

- As the playback head detects the error from the target track directly, it is possible to impose a stable servo regardless of mechanical changes in dimensions such as changes in temperature, with years, etc.

- As the fixed head is not necessary, the system can be made compact, leading to reduced costs.

Fig. 4.6 ATF Method

Next, how tracking errors are detected is described.

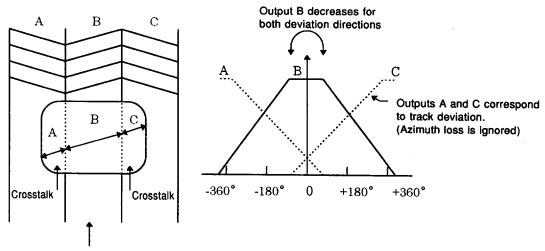

#### 4.2.2 Detection of Tracking Error

With the azimuth guard bandless recording method, the head rides onto the its own track as well as onto the adjoining tracks as shown in Fig. 4.7. Because only the signals of its own tracks are detected, only the signal level decreases when tracking errors occur, and therefore the direction of the deviation cannot be determined.

By detecting the signal level of adjoining tracks, the direction of deviation can be known easily just by monitoring these levels. The ATF method therefore records pilot signals for detecting tracking errors in adjoining tracks to detect the level.

If the frequency of the pilot signals is high, the output from the adjoining tracks decrease due to the azimuth effects and the characteristics of the tracking error deteriorates. While, if the frequency is low, the erasure rate deteriorates, resulting in deterioration of the overwrite characteristics. Consequently, the 130 kHz signal is selected as the pilot signal because it has both good tracking characteristics and overwrite characteristics.

With the guard bandless recording method, the signals of both adjoining spaces of the head are traced.

Fig. 4.7 Concept of ATF Method

#### 4.2.3 Features of DAT ATF

The features of the ATF method are as follows.

#### (1) Independent areas

• Sub-code after recording, etc. is possible

As the time-division process is performed, the reference timing is obtained by detecting the sync signal recorded on the track, providing high resistance to wow flatter and jitters.

#### (2) 2-point ATF

- · Optimum tracking is performed for linear deviation of the track

- If one ATF signal falls off the track due to scratches and dropout of the tape, it will be covered by the other ATF signal, enabling stable tracking and the performance of the error correction method to be displayed to the full.

- · Useful for improving linearity and variable speed playback

#### (3) Single frequency time divided pilot

• The pilot signal appears deviated time-wise from the adjoining tracks

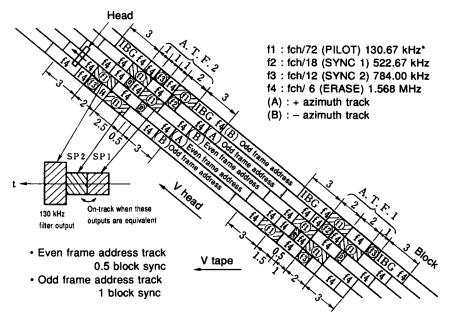

#### (4) 4-track completion type

• As shown in Fig. 4.8, four patterns, namely the pilot signal (f1), sync signals (f2 and f3), and erasure signal (f4) are repeated for every four tracks, to form a four-in-one track pattern.

f1: Pilot signal (130 kHz)

f2: + azimuth track (Head A) sync signal 1 (522 kHz)

f3: - azimuth track (Head B) sync signal 2 (784 kHz)

f4: Erasure signal (1.5 MHz)

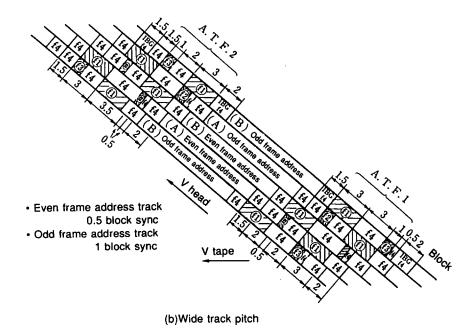

(a) Normal track pitch

Fig. 4.8 ATF Patterns

# **CHAPTER 5. SUB CODES**

This chapter describes DAT sub codes. The volume of sub codes of the DAT is about four times that of CDs. A wide variety of applications can be considered, and enhancement of operations is being made so that users can record complicated sub codes with recording and playback devices by themselves.

#### 5.1 Sub Code Format

Fig. 5.2 shows the recording format of the DAT sub codes.

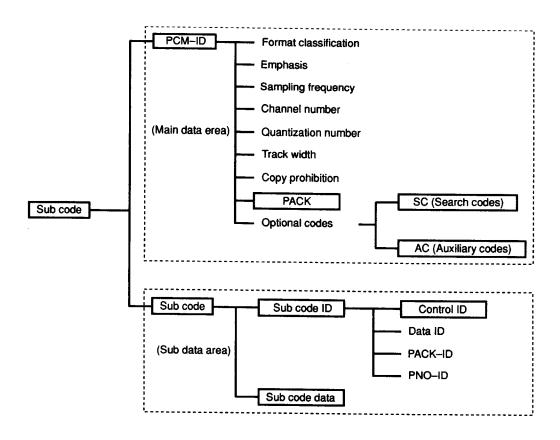

As shown in Fig. 5.1, there are two kinds of DAT sub codes-main data area and sub data area.

Fig. 5.1 Classification of Sub Codes

Fig. 5.2 Sub Code Recording Format

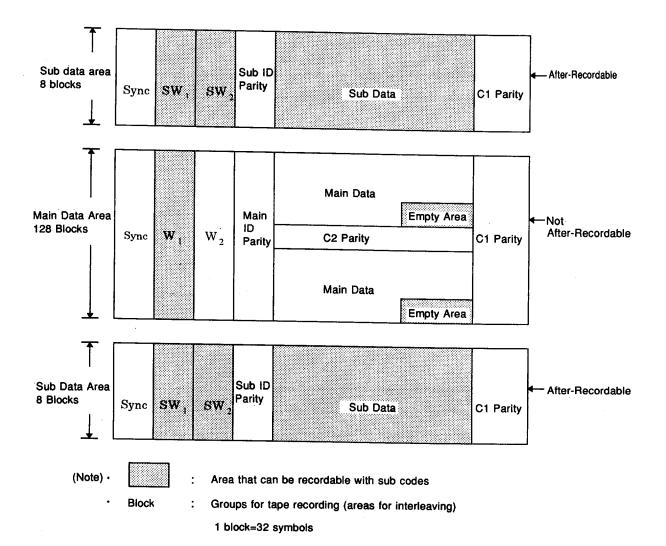

Areas that can be recorded with sub codes are the following three areas, as shown in Fig. 5.3.

- 1 Main data area W1

- 2 Empty area for main data in the main data area

- 3 Sub data area SW1, SW2 and sub data

Of these, only the sub data area 3 can be rewritten by after-recording.

The sub codes of the main data area and sub data area are described in the following in detail.

Fig. 5.3 DAT Sub Code Recordable Area

#### 5.2 Sub Codes of Main Data Area

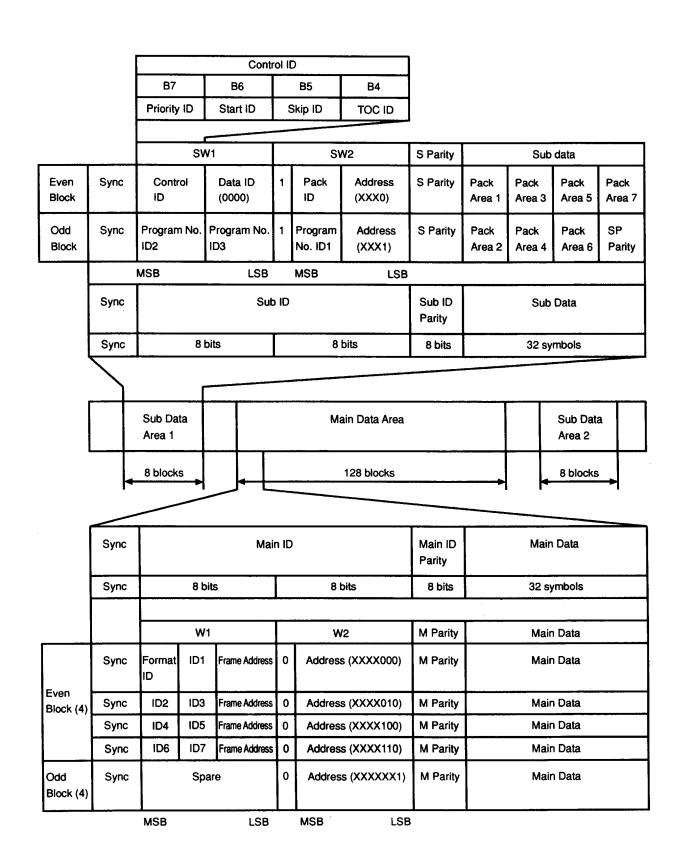

The sub codes in the main data are recorded in the W1 of the main ID and the empty area in the main data area. Fig. 5.4 shows the main ID recording format.

| Sync Signal |      | Main ID               |        |    |     |              |    |           | Main ID Parity |         |    |      | Ма      | in Data |    |    |  |

|-------------|------|-----------------------|--------|----|-----|--------------|----|-----------|----------------|---------|----|------|---------|---------|----|----|--|

| 8 bits      |      | 8                     | 3 bits |    |     | 8 bits       |    |           | 8 bits 32      |         |    | 32 9 | symbols |         |    |    |  |

|             |      |                       |        |    |     |              |    |           |                |         |    | ٠    |         |         |    |    |  |

|             |      | W1                    |        |    |     |              |    |           | W2             |         |    |      |         |         |    |    |  |

|             | В7   | В6                    | B5     | B4 | вз  | B2           | В1 | ВО        | В7             | В6      | B5 | В4   | В3      | B2      | B1 | во |  |

|             | Form | nat ID                | I      | )1 | Fra | ame Address  |    | 0         |                | Address |    |      |         |         |    | 1  |  |

|             | IC   | ID2 ID3 Frame Address |        |    | 0   | 0 Address    |    |           |                |         |    |      |         |         |    |    |  |

|             | II.  | <b>)</b> 4            | I      | 05 | Fra | rame Address |    | 0 Address |                | ss      |    |      |         |         |    |    |  |

|             | 10   | <b>)</b> 6            | IE     | 07 | Fr  |              |    | 0         | Address        |         |    |      |         |         |    |    |  |

Fig. 5.4 Main ID Format

Of the W<sub>1</sub> of the even address block, 4 bits are allocated to the sub codes of the FORMAT ID and ID 1 to 7, and important data is repeatedly recorded for 16 times every eight blocks. The sub codes in these blocks are recorded with data essential to playback the main data. The contents are shown in **Table 5.1**.

The 8 bits of the W1 of the odd address block are called optional codes and these are recorded with the same signals as the sub data area explained later. But because these cannot be after-recorded, the method of use is limited. As shown in **Fig. 5.1**, the optional codes are divided into search codes and auxiliary codes. The contents are shown in **Table 5.2**.

**Table 5.1 ID1 to 7**

| ID No. | Contents (Uses)    | Bit Allocation           |

|--------|--------------------|--------------------------|

| ID1    | Emphasis           | B5 B4                    |

|        |                    | 0 0 : Not used OFF       |

|        |                    | 0 1 : 50/15 μs ON        |

| ID2    | Sampling frequency | B7 B6                    |

|        |                    | 0 0 : 48 kHz             |

|        |                    | 0 1 : 44.1 kHz           |

|        |                    | 1 0 : 32 kHz             |

| ID3    | Channel no.        | B5 B4                    |

|        |                    | 0 0 : 2 ch               |

|        |                    | 0 1:4ch                  |

| ID4    | Quantization rule  | В7 В6                    |

| ļ      |                    | 0 0 : 16-bit linear      |

|        |                    | 0 1: 12-bit non-linear   |

| ID5    | Track pitch        | B5 B4                    |

|        |                    | 0 0 : Normal track mode  |

|        |                    | 0 1 : Wide track mode    |

| ID6    | Copy prohibition   | B7 B6                    |

| j      |                    | 0 0 : Permitted          |

|        |                    | 1 0 : Prohibited         |

|        |                    | 1 1 : Permitted for only |

|        |                    | one generation           |

| ID7    | For pack           | B5 B4                    |

|        |                    | Contents of pack         |

**Table 5.2 AC (Auxiliary Codes)**

| AC Item | Contents             |  |  |  |

|---------|----------------------|--|--|--|

| 0000    | No information       |  |  |  |

| 0 0 0 1 | Absolute time        |  |  |  |

| 0010    | Program time         |  |  |  |

| 0011    | Index time           |  |  |  |

| 0100    | Program no., others  |  |  |  |

| 0101    | Not used             |  |  |  |

| 0110    |                      |  |  |  |

| 0111    |                      |  |  |  |

| 1000    | Calendar information |  |  |  |

| 1001    |                      |  |  |  |

| 1000    | mod                  |  |  |  |

| 1001    | тос                  |  |  |  |

| 1010    | Catalogue code       |  |  |  |

| 1011    | Catalogue code       |  |  |  |

| 1100    |                      |  |  |  |

| 1101    | ISRC                 |  |  |  |

| 1110    |                      |  |  |  |

| 1111    | Not used             |  |  |  |

Next, the empty area in the main data area is described.

The main data is guarded very strictly by the C1 and C2 Reed Solomon codes, as described in Chapter 4. It is an area in which data can be recorded and played back most reliably.

As this area cannot be after-recorded nor subjected to high speed search, it is suitable for recording a large volume of data such as software tapes.

For example, the empty area for the main data when the sampling frequency is 44.1 kHz is has a volume of 1.5 to 3 times the sub codes of CD.

#### 5.3 Sub Codes of Sub Data Area

The sub codes of the sub data area has the widest application because it can be after-recorded.

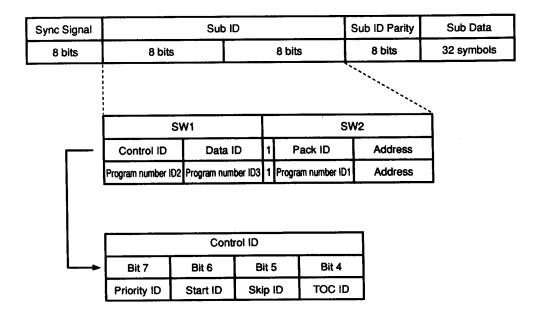

Fig. 5.5 shows the format of the sub ID. In the sub data area, the SW1, SW2, and sub data area of the sub ID are used. As the sub codes in the sub data area are recorded with data required for high speed search, the sub ID has a length of 32 bits including the sync signal and parity for check. This is because during high speed search, as the head crosses the tape diagonally, and consequently some parts of the data will always be missing if it is too long, it is essential for the data to be complete in itself in small units.

Fig. 5.5 Sub ID Format

Table 5.3 shows the relation between the IDs and their roles.

Of these IDs, the control ID is especially important. The control ID is recorded with the start ID and the shortening ID that users utilize the most frequently.

- ① As its name implies, the start ID is used to indicate the start of a music, and plays a major role in high speed search. As there is no way to estimate where the start ID is recorded, and as there is a need to read it steadily during high speed search, the start ID is recorded for 9 seconds (LP mode: 18 seconds).

- ② The shortening ID (also called skip ID) is useful for cutting the unrequired portions of the recorded tape.

Table 5.3 SUB ID

|             |           | Contents                                          |              |                                                    |  |  |  |  |  |

|-------------|-----------|---------------------------------------------------|--------------|----------------------------------------------------|--|--|--|--|--|

| Data ID     | Indicates | Indicates how to use the sub ID, 0000 = For audio |              |                                                    |  |  |  |  |  |

|             | B4        | TOC ID                                            |              | Indicates the presence/absence of TOC              |  |  |  |  |  |

| Control ID  | В5        | Shortening ID (Skip ID) Start ID                  |              | Indicates the start of unrequired portions of tape |  |  |  |  |  |

|             | В6        |                                                   |              | Indicates the start of program                     |  |  |  |  |  |

|             | В7        | Priority ID                                       | )            | Indicates the priority of sub codes                |  |  |  |  |  |

|             | ID1       | ID2                                               | ID3          |                                                    |  |  |  |  |  |

|             | 0         | 0                                                 | 0            | No number                                          |  |  |  |  |  |

| Program NO. | 0         | 0                                                 | 1            |                                                    |  |  |  |  |  |

| J           |           | to                                                |              | Program number 1 to 799                            |  |  |  |  |  |

| ID 1 to 3   | 7         | 9                                                 | 9            |                                                    |  |  |  |  |  |

| 1 10 5      | 0         | A                                                 | A            | Undefined number "1010"                            |  |  |  |  |  |

|             | 0         | В                                                 | В            | Read-in area "1011"                                |  |  |  |  |  |

|             | 0         | E                                                 | E            | Read-out area "1110"                               |  |  |  |  |  |

| Pack ID     | Indicates | the pack num                                      | ber of the s | sub data area (0 to 7)                             |  |  |  |  |  |

### 5.4 Sub Codes of Sub Data Section

This area is imposed with the C1 Reed Solomon code completed in 2 blocks, just like the main data area. Various types of sub codes can be recorded in small units. In addition, a pack made up of 64 bits which can also be read i high speed search is used. The pack is, as shown in **Fig. 5.6**, located at seven spots covering two blocks, and will be recorded for the number defined by the pack ID.

An example is shown in Fig. 5.7. The pack is first made up of 4 bit (B7 to B4) items, then a 52-bit data area, and finally 8-bit parity.

|     | В7     | В6     | В5     | В4 | В3 | B2 | B1 | В0 |

|-----|--------|--------|--------|----|----|----|----|----|

| PC1 | Pack   | item   |        |    |    |    |    |    |

|     | 4 bits | 8      |        |    |    |    |    |    |

| PC2 |        |        |        |    |    |    |    |    |

| PC3 |        |        |        |    |    |    |    |    |

| PC4 |        |        |        |    |    |    |    |    |

| PC5 |        |        |        |    |    |    |    |    |

| PC6 |        |        |        |    |    |    |    |    |

| PC7 |        |        |        |    |    |    |    |    |

| PC8 | Pack   | parity | 8 bits |    |    |    |    |    |

|     | В7           | <b>B</b> 6                  | B5 | B4   | В3     | B2   | <b>B</b> 1 | <b>B</b> 0 |

|-----|--------------|-----------------------------|----|------|--------|------|------------|------------|

| PC1 | Pack         | item                        |    |      |        | Prog | gram n     | o. 1       |

|     | 0            | 0                           | 0  | 1    | 0      |      |            |            |

| PC2 | ]            | Program no. 2 Program no. 3 |    |      |        | 3    |            |            |

| PC3 | Index no.    |                             |    |      |        |      |            |            |

| PC4 | Hours (PH)   |                             |    |      |        |      |            |            |

| PC5 | Minutes (PM) |                             |    |      |        |      |            |            |

| PC6 | Seconds (PS) |                             |    |      |        |      |            |            |

| PC7 | Frame        |                             |    |      |        |      |            |            |

| PC8 |              |                             |    | Pack | parity |      |            |            |

Fig. 5.6 Pack Format

Fig. 5.7 Example of Pack (When pack item is 0001)

By adopting such a structure, data completed in a short block even during high speed search, enabling reading and checking of errors. Multiple recording is performed to improve precision and reliability. By changing the 4-bit item area, the pack can be recorded with various data such as;

- Program time

- · Absolute time from head of tape

- TOC

**Table 5.4** shows a list of the items currently available.

Table 5.4 List of Pack Items

| Pack Item | Contents             |

|-----------|----------------------|

| 0001      | Program time         |

| 0010      | Absolute time        |

| 0 0 1 1   | Running time         |

| 0100      | тос                  |

| 0101      | Calendar information |

| 0110      | Catalogue cord       |

| 0111      | ISRC .               |

| 1000      |                      |

| to        | Not used             |

| 1111      |                      |

# **CHAPTER 6. DAT CASSETTE AND TAPE**

### 6.1 Features of DAT Cassette

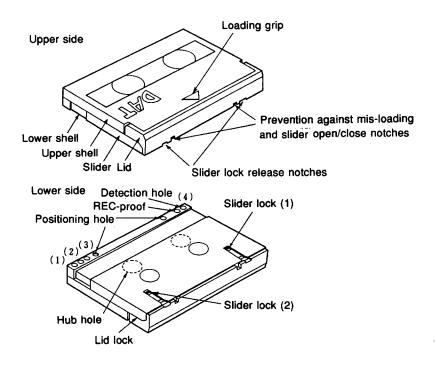

The DAT cassette is a new type of cassette intended for the DAT system. It is completely different from compact cassettes and 8 mm VTR cassettes using the rotary head method.

The features of the DAT cassette are as follows.

- ① Flangeless cassette with external dimensions of 73x54x10.5 mm

- 2 Continuous recording time of two hours with a standard tape

- 3 Completely sealed off structure with use of slider to seal off hub hole, and front cover lock mechanism

- Hub brake mechanism linking to front cover to prevent slacking of tape.

- (5) Prism type tape end detection mechanism effectively using guide pin storage area inside cassette

- 6 Reusable tape rec-proof mechanism, and four identification holes

- ① Loading grip for drawing in cassette

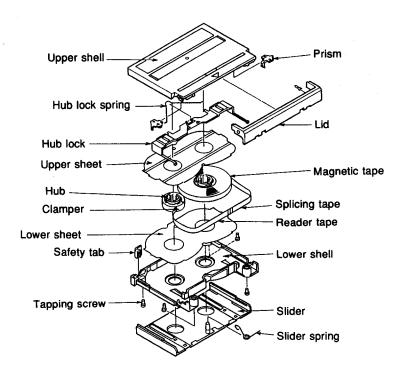

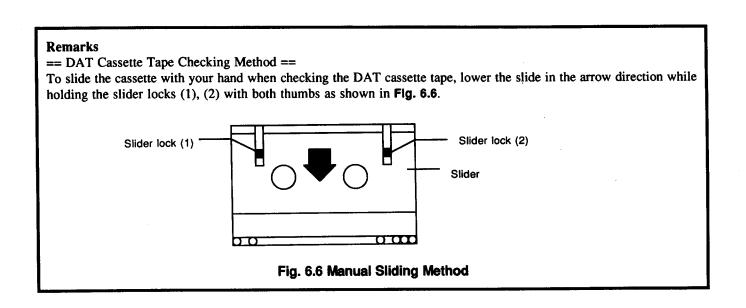

#### 6.2 Structure of DAT Cassette

Fig. 6.1 shows the external structure of the DAT cassette and Fig. 6.2 shows the internal structure.

The following describes the four holes for identification and one hole for rec-proof detection shown in **Table. 6.1**. These four identification holes play an enormous role in the operations of the system, and opening or closing them unintentionally may result in improper operations of the system.

Table 6.1 Purpose of Use of Hole

| Hole (1) | Hole (2) | Hole (3) | Contents                                         |

|----------|----------|----------|--------------------------------------------------|

| 0        | 0        | 0        | Metal tape or equivalent/standard tape thickness |

| 0        | 1        | 0        | Metal tape or equivalent/thin tape               |

| 0        | 0        | 1        | Wide track tape/standard tape thickness          |

| 0        | 1        | 1        | Wide track tape/thin tape                        |

| 1        | ×        | ×        | Not specified (For future use)                   |

| Hole (4) | Contents                              |

|----------|---------------------------------------|

| 1        | Prerecorded tape (Playback only tape) |

| 0        | Blank tape                            |

Note) "1" Open, "0" Close

Fig. 6.1 External Structure of DAT Tape

Fig. 6.2 Internal Structure of DAT Tape

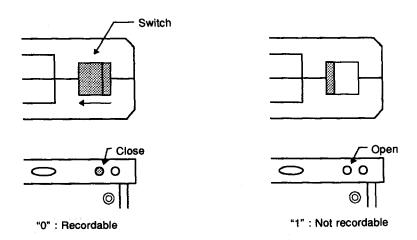

The rec-proof hole can be switched with a switch as shown in Fig. 6.3 so that it can be used over and over again.

Fig. 6.3 Rec-Proof Switch

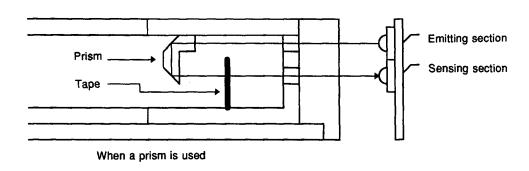

Next, the mechanism of tape end detection is described. With the DAT system, this tape end detection is performed using the optical detection method. A transparent reader tape (passes light) is attached at the start and end of the tape. The magnetic tape does not let light pass. The DAT tape is incorporated with a prism. As shown in **Fig. 6.4**, the light from the light emitting section passes through the tape at the start and end of the tape and reaches the prism for the light sensing section to detect "tape-top" or "tape-end" via the prism.

Fig. 6.4 Tape End Detection Method 1

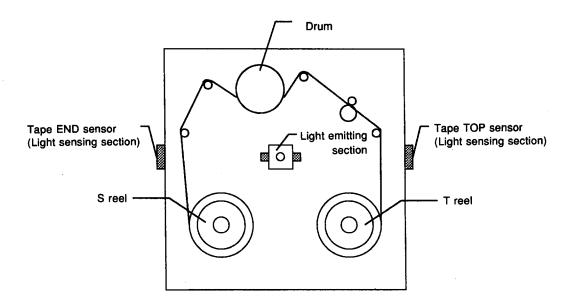

Recently, in some models, instead of using a prism inside the tape, the light emitting section is set at the center of the mechanism section and the light sensing section is set both ends of the mechanism section as shown in **Fig. 6.5** to detect the "tape-top" and "tape-end" using the light detection method.

Fig. 6.5 Tape End Detection Method 2

# **CHAPTER 7. DIGITAL AUDIO INTERFACE**

## 7.1 Digital Audio Interface

Most digital audio equipment such as CD players, BS tuners, PCM processors, DAT systems, etc. are equipped with a digital output (digital out), which cannot output nor input signals at all if the format, sampling frequency, input/output connector, etc. do not match.

For this digital signal output to be compatible, the digital audio interface standard\*1 was created.

\*1 : Adopts the serial transmission signal format conforming to the "digital audio interface format" of IEC958 (IEC: International Electrotechnical Commission).

#### 7.2 Format

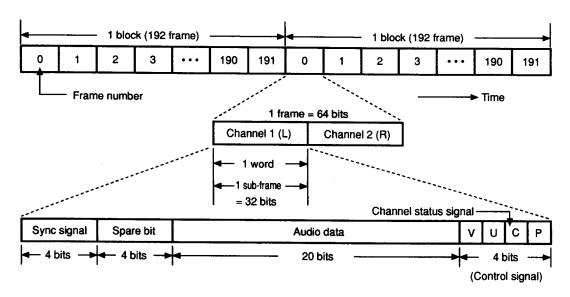

Fig. 7.1 shows the digital output signal format. The top part of Fig. 7.1 shows how the transmitted signal is arranged by time. The serial-transmitted digital signals are composed of 64 bits, in which the pair of Lch and Rch 1 sampling information is called "frame".

As shown in the middle part of Fig. 7.1, the information of one channel is composed of half of this one frame-32 bits. The 1 sampling information of either channel is called "sub-frame" or "word". Therefore, two sub-frames of Lch and Rch form one frame.

As shown in the bottom part of Fig. 7.1, the first four bits of the sub-frame are the sync signal, the next four bits are spare bits, the following twenty bits form the audio data area, and the last four bits, which are four types of 1-bit codes (V, U, C, and P), are the control signal which carries signals accompanying the data such as copy prohibition and emphasis.

Fig. 7.1 Digital Out Signal Format

#### 7.2.1 4 Types of Control Signal

**Table 7.1** shows details of the 4 types of control signals.

Table 7.1 Details of Control Signal

|   | Name           | Details                                                                                                               |  |  |  |

|---|----------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|

| V | Validity       | Flag which shows whether the data is effective and consequently whether it contains errors or not                     |  |  |  |

| U | User's bit     | Used for transmitting the sub code information on each equipment                                                      |  |  |  |

| С | Channel Status | Input with control information such as the ON/OFF of emphasis and copy prohibition information                        |  |  |  |

| P | Parity         | Used with the aim of detecting errors during transmission and keeping the polarity of the sync signal always the same |  |  |  |

The "C" channel status signal is described below as it plays an important part in the SCMS (serial copy management system) described later.

### 7.2.2 Channel Status Signal

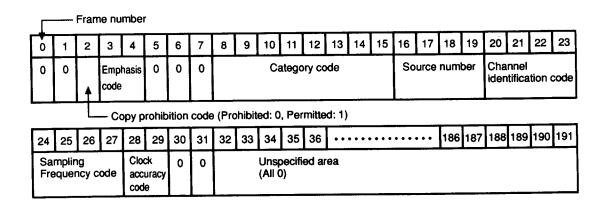

Fig. 7.2 shows the channel status signal format.

One block of the digital audio interface format signal contains, as shown in Fig. 7.1, 192 frames from frame 0 to frame 191. The "C" signal in each frame contains one bit each. Consequently, as shown in Fig. 7.2, for the channel status signal, 192 bits form one set. The details are as follows.

- ① Copy prohibition code is 1 bit

- 2 Code showing ON/OFF of emphasis is 2 bits

- 3 Code showing type of signal source called category code is 8 bits

- 4 Source number is 4 bits

- **5** Code showing channel number is 4 bits

- (6) Bits showing sampling frequency is 4 bits

- ① Code showing accuracy of transmission clock of the transmission side is 2 bits

Fig. 7.2 Channel Status Signal ("C") Format

### 7.2.3 Category Codes

Category codes are provided for the reception side to identify what is the transmission side of the digital signal. **Table 7.2** shows the main public digital audio source category codes.

| Table 7.2 Example of | <b>Consumer Use</b> | <b>Audio Categor</b> | v Code |

|----------------------|---------------------|----------------------|--------|

|----------------------|---------------------|----------------------|--------|

| Category Name | Category Code |

|---------------|---------------|

| General       | 00000000      |

| CD            | 1000000       |

| PCM processor | 01000000      |

| DAT           | 11000000      |

| DAT-P         | 11000001      |

| MD            | 10010010      |

| MD-P          | 10010011      |

Amongst these, "general" is used for sources which have no corresponding category codes, products produced before the category codes were fixed, and sources for which the presence/absence of rights information was unknown (whether can copy or not) with the analog signal originally such as signals which have passed through the AD converter.

# **CHAPTER 8. OUTLINE OF SCMS**

The SCMS (Serial Copy Management System) is, as its name implies, a system which controls serial copy digitally by DAT.

Regarding DAT digital copy, in July 1989, a proposal for a resolution based on the agreement of those concerned was announced, and from May 1990, on receiving official notification from the Ministry of International Trade and Industry, this method was adopted for products produced thereafter.

# 8.1 SCMS Method in Different Uses

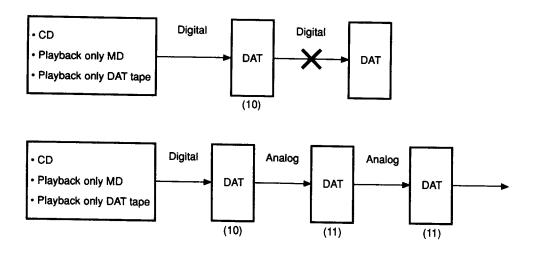

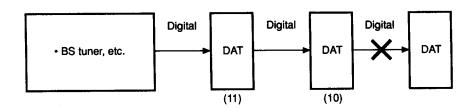

The following describes the different uses of the SCMS method. (1)Digital copy from playback only MD and playback only DAT tape

Although digital outputs from CDs, playback only MDs, and playback only DAT tapes contain copy prohibition codes, only the first generation is allowed digital recording, while copy is not allowed for generations thereafter.

There is no restriction on copying of digital-recorded media with the analog input/output.

Fig. 8.1 Digital Copy from Software Tape

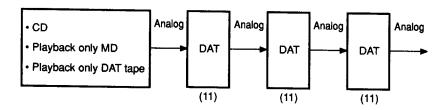

#### (2) Analog Copying

Copied tapes from analog sources are taken as DAT music tapes with copy prohibition codes, but there are no restrictions on copying using the analog input/output.

Fig. 8.2 Analog Copying from Software Tapes

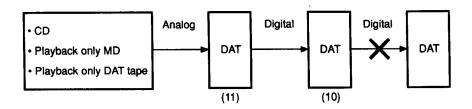

3)Digital Copying from Analog Copied Tapes

The analog signal output only has an audio signal and no copy prohibition codes, etc. This input can be recorded with the DAT. But tapes recorded with this method are taken as DAT music tapes containing copy prohibition codes regardless of whether there are inputs or not, because there is no method available for identification. Consequently, digital copying from such tapes is possible, but digital copying after that is not allowed. For analog input/output, like CDs of digital source, microphones, FM tuners, analog recorders, etc. are also handled in the same way regardless of the digital sources.

This means that once a signal which has passed through an A/D converter is recorded by DAT, this copy tape will become a DAT music tape with copy prohibition codes.

Fig. 8.3 Digital Copying from Analog Copied Tapes

(4) Digital Copying when Category Codes are "General" (BS tuners, etc.)

When category codes are "general", digital copying can be performed for the second generation as well even if the tape contains copy prohibition codes. And, even if copying is permitted, digital copying can be performed only to the second generation.

Fig. 8.4 Digital Copying when Category Codes are "General"

(Note) The ( ) in the figure indicate the ID6 bits.

00: Digital copying permitted 10: Digital copying prohibited

11: Digital copying permitted only for 1st generation

## 8.2 Processing Routine of SCMS Method

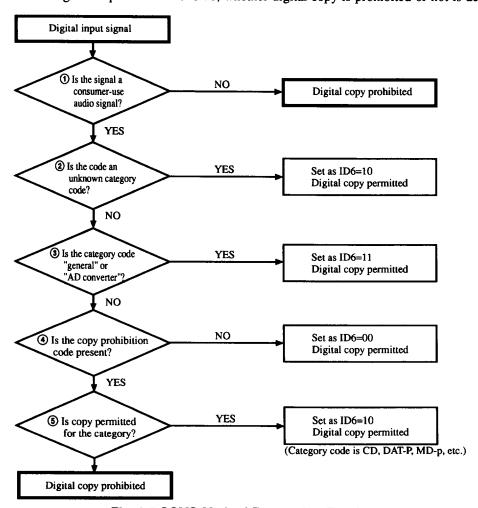

Fig. 8.5 shows the digital copy processing routine of the SCMS method

For digital inputs, digital copy prohibition/permission and ID6 are determined by this routine. For digital copy to be permitted, ID6 must be recorded on the tape.